基于STM32实现的软件无线电收发系统设计

本文为鄙人的本科毕业设计,在此对文章略作摘录记录于此。本设计存在诸多不成熟的地方,参考时请务必仔细甄别&思考,欢迎讨论。

摘要

本设计拟在STM32上通过软件无线电平台实现一个射频无线电收发平台,该平台可以用于无线电信号的调制与解调,最终确定了发送端的零中频架构与接收端的低中频架构,并同时确定了发送板、核心板、接收板的系统结构。

硬件设计部分主要涉及滤波器设计、阻抗匹配、信号屏蔽与信号调理电路。最终选用巴特沃斯滤波器作为接收机的前端滤波器,RC滤波器作为ADC的抗混叠滤波器;对于阻抗匹配主要涉及微带线与共面波导两种结构,文中分别予以介绍与计算;对于信号屏蔽部分主要介绍了合理接地与可靠退耦两种方法,通过良好的设计来保证信号的可靠传输;信号调理部分涉及外部输入输出信号的阻抗、功率与频率匹配,本设计中主要通过运算放大器来实现调理。

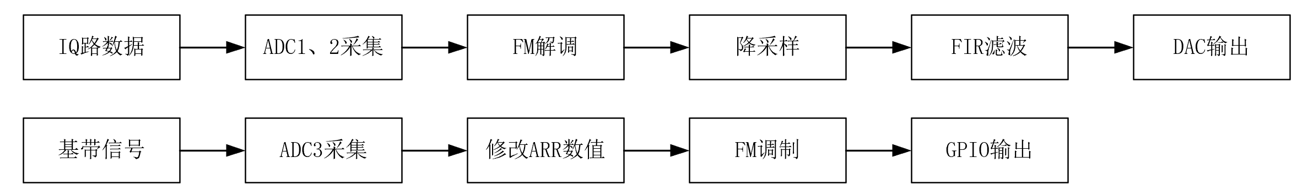

软件设计部分主要包括信号的调制解调、下采样、滤波与人机交互。其中FM信号的解调通过差分近似微分实现,信号的调制通过控制PWM输出定时器的自动重装载值实现,下采样通过定点取均值实现,滤波器通过FIR滤波器实现。人机交互部分使用到OLED、按键、扬声器、3.5mm耳机孔等外设,通过软件逻辑实现合理的人机交互。

在课题的最后,还使用到了示波器、频谱仪、信号发生器与网络分析仪来对设计进行分析。通过分析输出信号频谱、滤波器幅频特性、天线驻波比与解调路径波形频谱等指标,最终确定本设计的总体性能指标。通过方案设计、软硬件实现、测试验证等步骤,本课题最终实现了设计的全部流程。但受限于成本、仪器指标、开发周期的限制,本设计仍有诸多不足之处。

1、绪论

构建一个低成本与高灵活度的软件无线电平台不仅能够为射频电路的工程实现提供启发,还能为教学实验与科研工作中的理论验证提供敏捷的实验开发平台。本课题便是在此背景下设计的一个面向教学实验工作的软件无线电开发平台,能够帮助使用者以最低的开发成本进行理论设计的实现与测试。

研究现状

完整的软件无线电系统通常由模拟前端与基带处理单元组成,其中模拟前端用于信号的上下变频、滤波、放大、相位捕获等操作,基带处理单元则主要进行数字基带信号的产生与预处理。近些年来,随着软件无线电应用范围的不断扩展,市面上也出现了许多经典的应用架构与商用方案。本节将会对这些典型的设计架构进行概述,并提出一些现有架构的局限与问题。

- ZYNQ+AD936X:目前最为成熟的软件无线电应用架构,该架构不仅仅存在于终端产品的应用中,也被广泛应用于基站中。该方案借助ADI公司的AD936X芯片实现了单片集成的射频前端处理(如下图1-1所示),即包含功率放大、混频、滤波、采样、转换等步骤。该芯片可以帮助开发者获得最好的模拟链路一致性与最低的链路调试成本,进而大大缩短产品开发与量产成本。

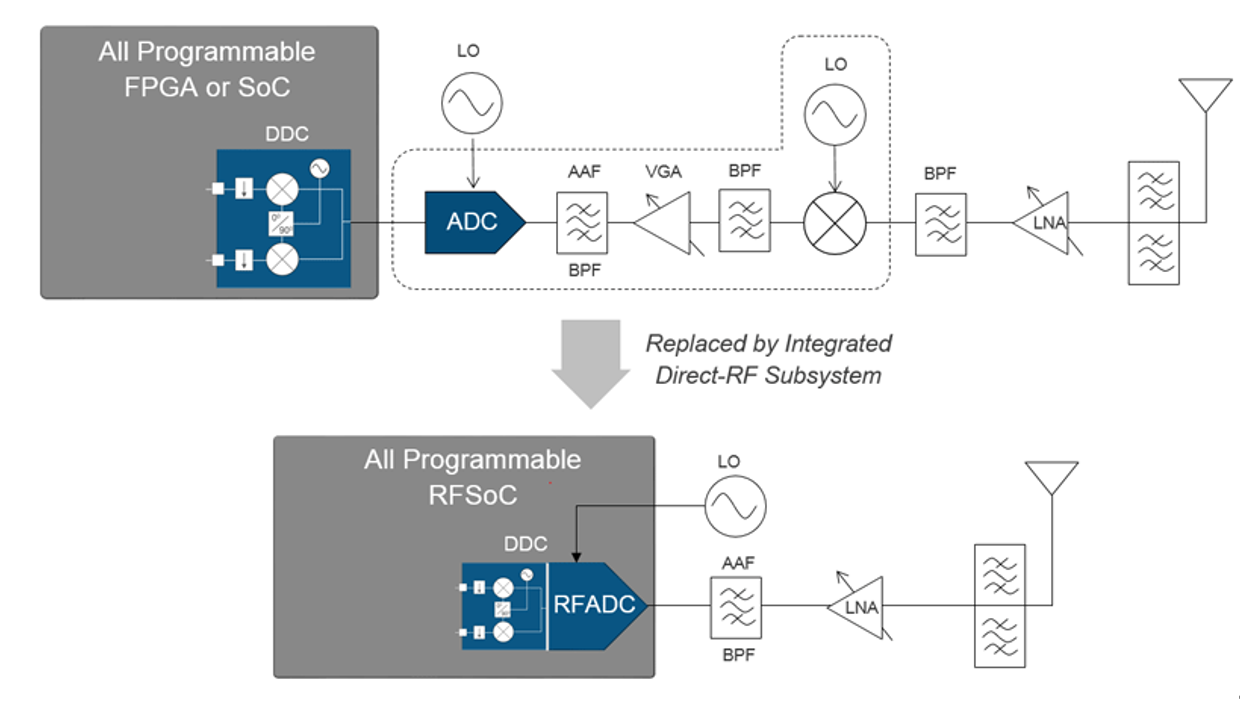

ZYNQ UltraScale+ RFSoC:目前性能最强的软件无线电单片解决方案(如图1-1所示),借助FPGA内置的超高速ADC与DAC实现单片射频域的信号接收与发射。在实际应用中,仅仅需要搭建极为简单的放大与滤波前端电路,便可实现一个极高带宽的无线通信系统。目前已经量产的高端RFSoC可以在单芯片内集成8通道5Gsps的高速ADC、16通道9.85Gsps的高速DAC与930K的逻辑资源。在保持超高采样率的同时,ADC与DAC也拥有14bit的分辨率,能够为基带信号处理提供极佳的信噪比。

- PC+分立元件:该方案借助分立元件来搭建信号的前端处理电路,基带的信号处理则通过USB或PCIe交由PC端处理。在单片的射频收发器没有量产之前,市面上的主流方案均是采用分立元件作为前端处理电路,对射频域的信号进行调理与采样。

课题任务

为了能将目前商用的软件无线电方案落地到教学实践中,就需要对目前的方案成本进行优化,开发流程重新进行设计。以保证能够以最低的成本,最短的开发周期来进行算法部署于实践。因此,本课题的具体任务如下:

构建一个低成本软件无线电收发系统,接收部分覆盖0-500M,发射部分覆盖0-200M。发射部分可以产生模拟调制与数字调制的信号,并通过天线发射;接收部分可以解调经过调制后的信号,该信号可以是自然环境中的AM、FM信号,也可以是SDR发送的ASK、FSK、PSK等信号。若基带信号为模拟信号,则将其通过扬声器播放;若为数字信号则应当将其解调后在OLED上显示。具体要求如下:

- 低成本:单套成品的成本价格控制在100元左右,开发成本控制在1000元以内;

- 模块化:成品的系统的设计应当使用模块化设计,即要求核心板和射频收发板分离并可随时插接;

- 高灵活:要求系统可以同时具备模拟与数字信号的收发能力,用户也可以便捷地进行频点变更与参数修改;

- 低代码:具备一定的教学与实验意义,能够让使用者轻松地进行框架或细节上的实现。同时,该课题设计用于可以方便地进行快速地开发应用,便于比赛时的使用;

- 宽频段:可以在设计的频率范围内进行射频收发测试并拥有良好的模拟链路特性,进行信号发射时应当注意避让主要业务的频谱范围。

结构安排

- 绪论:简要描述目前SDR的研究背景与本课题的最终任务;

- 方案设计:介绍并比较本课题所选择的架构、器件与工具链;

- 硬件设计:介绍项目推进过程中遇到的阻抗匹配、滤波、信号调制等问题;

- 软件开发:主要涉及基带下的调制解调与信号处理,包含FIR滤波、FM调制解调,以及一系列内部外设&外部芯片的驱动与软件架构;

- 测试与验证:使用诸多仪器来对设计进行合理性与可靠性验证;

- 结论:总结全文,提出未来的优化方向。

方案设计

在课题项目的具体实施之前,需要首先对技术路线、系统框架与元件选型进行评估与初步设计。其中技术路线的选择决定着整个系统的结构与功能实现方式;系统框架部分则要求功能的合理划分以满足低成本、模块化与高灵活的要求;元件选型部分则要求综合考虑成本、供货、开发周期等因素,最终为各个功能模块选择合适的解决方案。

技术路线

基带信号在通信系统中常代指没有经过调制的原始信号,该信号可以是经由模拟前端处理的模拟信号,也可以是由基带单元发送的数字信号。出于提高传输效率,方便复用频谱等原因,通信过程中往往会将信号进行调制。落实到工程实现当中,基带信号的发射往往还要经过一次上变频操作,因此本节所讨论到的通信架构便是描述如何对基带信号进行有效发射与接收的结构。

现代通信系统中常用的通信架构分为直接低通采样,射频带通采样与中频低通采样三种,下文予以分别介绍。

直接低通采样

在实际的通信过程中,为了使基带信号能够有效地发射出去,常常将基带信号加在高频载波上再进行发射。直接低通采样即要求直接对上变频后的信号进行采样,此时的采样率应当至少大于2倍的载波最高频率。诸如Kiwi SDR、RFSoc与PITAYA等方案均是采用该架构,通过一个极高速的ADC直接进行射频信号采样。

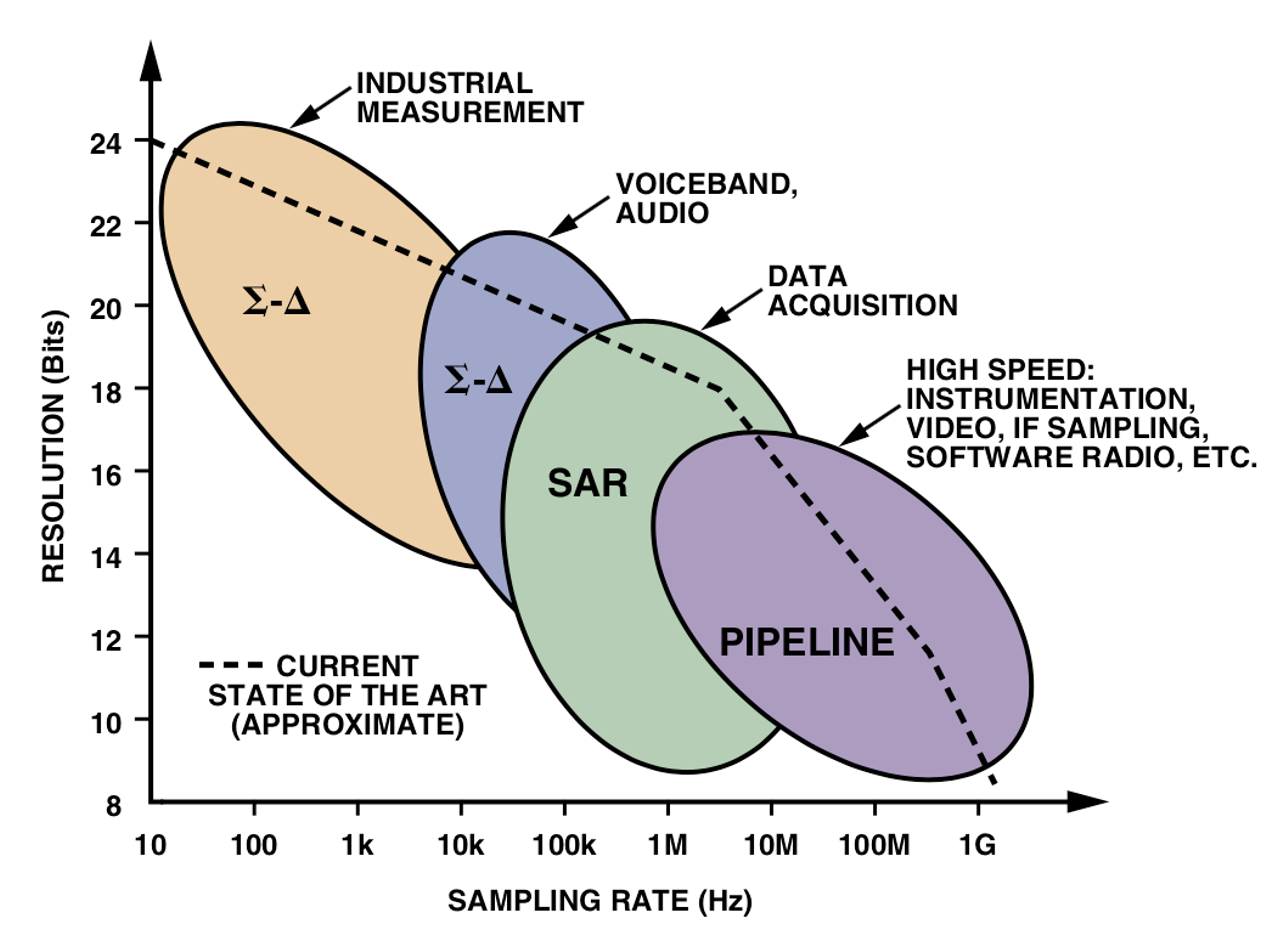

如图2-1所示,当采样率足够高时,ADC的有效位数往往不尽如人意,这就使得信号的信噪比与动态范围受限。信噪比上的差异会直接体现在星座图上,会影响对高阶调制信号的接收与解调。受限于器件性能与成本的限制,直接低通采样在高频软件无线电中应用范围较少。

射频带通采样

如上文所述,最终通过天线发射出去的信号是通过载波上变频的信号,携带有效信息的仍为基带信号,故在此可以仅考虑对基带范围内的信号进行采样。带通采样定理的本质是通过ADC的采样频率$F_s$对高频信号不断地进行下变频,将其变频到基带频率范围内便可实现信号的等效低通采样。

但在信号的带通采样时,基带加在射频信号(中心频率$F_c$)上,而在$0-F_c+F_s$的范围内仍可能存在其他干扰信号,使用$F_S$直接下变频将会造成混叠。故带通采样时,常要求使用带通的抗混叠滤波器对信号进行滤波后再进行采样,在改变载波频率时还需要改变滤波器的中心频率,灵活性较差。故该架构仅适用于频率固定的应用,比如拥有完整规范的802.11与LTE。同时由于进入ADC的信号频率较高,故对ADC的模拟带宽与前端保持器的要求较高,不易实现较高频率下的带通采样。

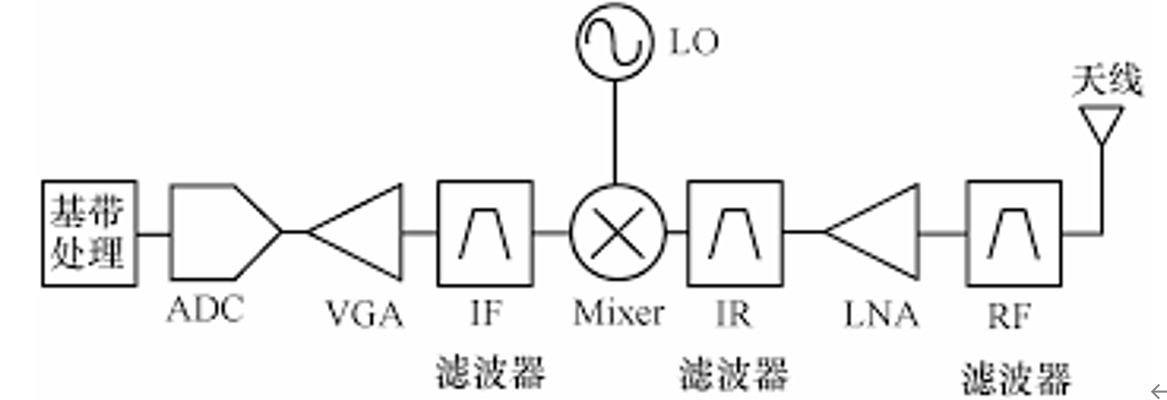

中频低通采样

前文所述的两种架构,均是使用ADC对射频信号采样,在实际应用中也可考虑通过本振产生的信号对射频信号进行下变频,在不改变有效信号的同时降低载波频率,进而降低对ADC的性能要求。经过下混频后的信号载波频率较低,此时的采样称为中频采样。根据中频频率的高低又可分为高中频、低中频与零中频三种架构,具体由混频后的中频频率决定。

高中频

该种架构的设计类似于超外差收音机,典型地有AM接收机中频465KHz,FM接收机中频10.7MHz。在进入IQ解调器之前,就已经完成了信号由射频到中频的转换。这种架构在基带部分还需要进行混频滤波器等操作,会提高系统的噪声系数并降低集成度,但拥有较高的接收动态范围。

低中频

与写作顺序不同地是,低中频接收机是为了解决零中频接收机直流偏置与噪声问题而出现的。这种架构将射频信号下变频到接近直流的低频信号,从而去除了直流偏置,同时能够更方便地进行信号的载波恢复。

零中频

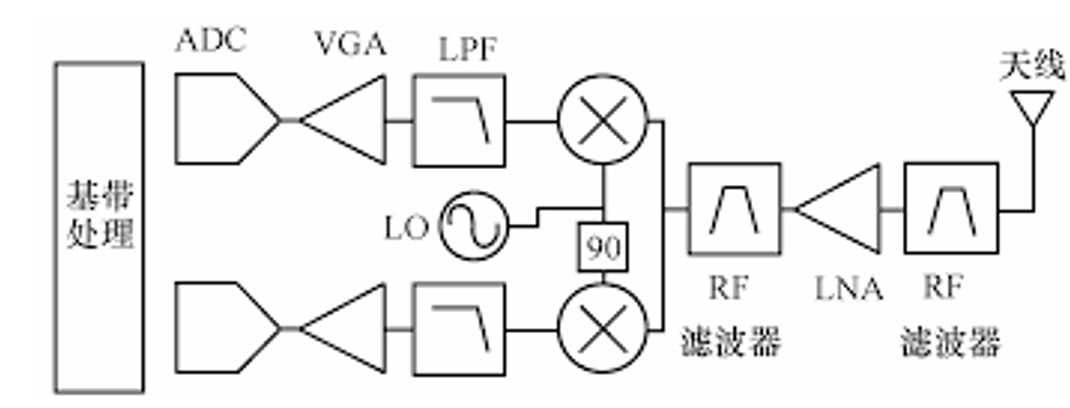

零中频架构要求信号的中频频率为$0Hz$,既有$F_{LO}=F_C$,经过零中频接收机后输出的信号为基带信号。由于本振频率与信号的载波频率相等,故常会产生本振泄露现象,经过混频后会在输出端产生直流偏置,进而造成后端放大器的饱和与ADC的量程缩限。同时由于IQ两路的本振存在不平衡度,使得最后的信号解调会受到影响。虽然零中频架构存在诸多缺点,但其仍被广泛应用于现代通信的发射与接收机当中去。一个典型的零中频接收机的示意图如图2-2所示。

在本设计中,接收机部分主要采用零中频架构并通过集成芯片进行信号处理,在提高集成度的同时减少因为分立元件的不一致性而带来的直流偏置与IQ不平衡;发射部分则采用低中频的结构,这种架构可以更好地对信号进行分析处理并提高灵活度。

结构划分

考虑系统设计的低成本、模块化与高灵活度的要求,本设计拟采用子母板的形式来根据功能进行硬件设计。硬件结构上大致划分为发送板、接收板与核心板,其中发送与接收板用于信号的收发调理,核心板用于基带信号的调制解调与用户操作。本设计的原理框图如图2-3所示,该图主要用于描述设计总体框架,具体的信号流图在选型完成后给出。

接收板

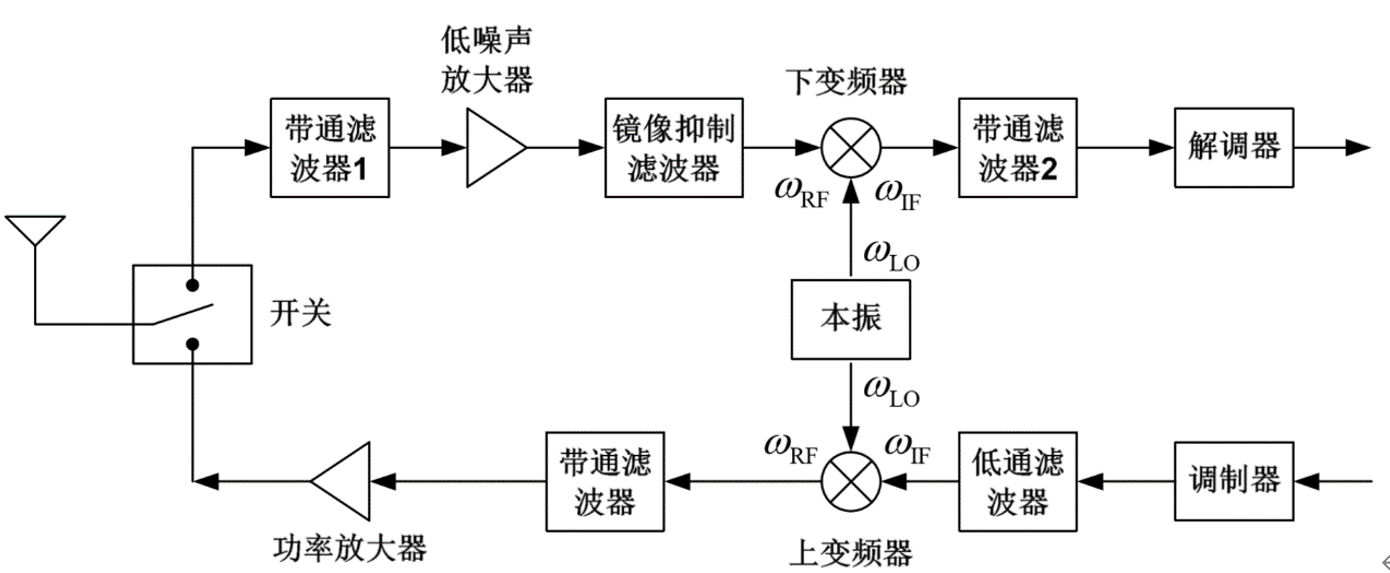

接收板作为射频信号采集的子板,能够实现模拟射频信号到模拟基带信号的转换,在该路径上我们借助集成前端芯片来实现零中频的采样架构。一个标准的射频接收机结构包括有天线、LNA(低噪声放大器)、LO(本地振荡器)、混频器、滤波器与中频放大器等结构,最后下变频到零频处的信号经由连接器输出。经典的模拟链路示意如图2-4所示。

在上图所示的模拟链路设计中,需要重点关注与介绍如下部分:

- 天线:进行无线信号的接收,一般而言要想实现信号的有效接收与传输需要保证天线尺寸能与无线电波长相比拟。典型地有: $L=\lambda/4$,其中$L$为天线长度,$\lambda$为无线电波的波长。

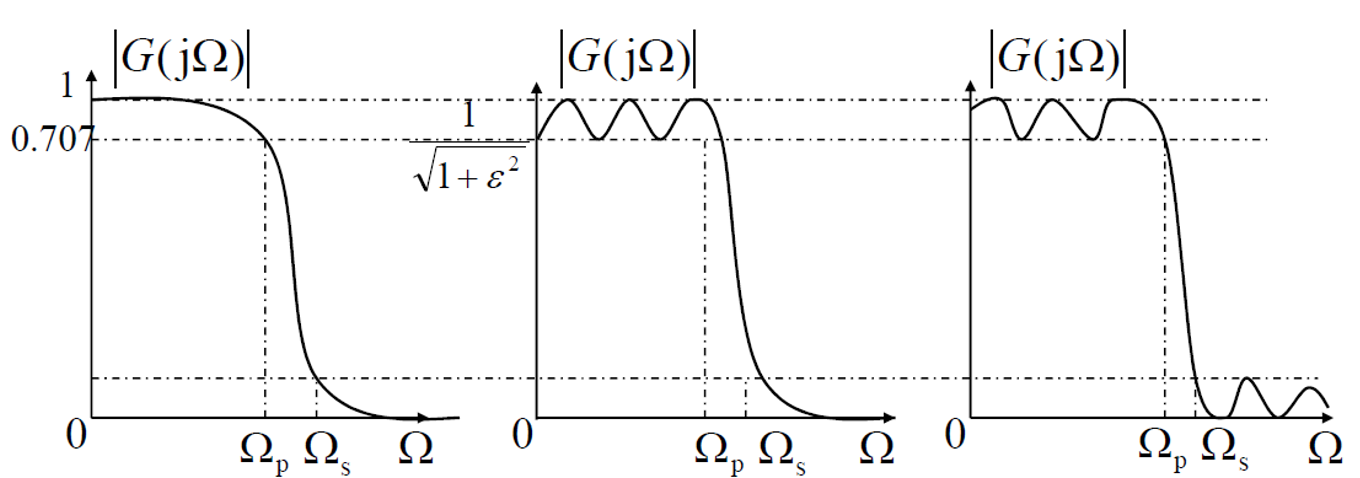

RF前端滤波器:进行干扰信号与噪声信号的滤除,由于自由空间中的无线电频谱被各种通信业务占用,因此要想以最佳的信噪比获得有用信号,就必须用滤波器屏蔽掉无用频段的信号。同时由于需要对空间中微弱的无线信号进行放大,一些较强的信号就很容易超过放大器的线性范围,使得对有用信号的放大倍数降低。因此接收端的模拟滤波器在提高信噪比,降低干扰方面有着重要的作用。常用的模拟滤波器有Butterworth型、Chebyshev型、Bessel型与Elliptic型。其中Butterworth型滤波器拥有平稳的幅频特性,阻带下降较慢;Chebyshev型则拥有较快的下降特性,但通带内有纹波;Bessel型则拥有线性相位特性与最平坦的幅频响应;Elliptic滤波器则在阻带内拥有最快的下降特性,但通阻带均有纹波。使用MATLAB绘制滤波器频谱特性,如图2-5所示,图中从左到右依次为巴特沃斯滤波器、切比雪夫I型滤波器与椭圆滤波器。

- 低噪声放大器:放大空间中微弱的电磁信号,使其能够在基带上通过ADC进行采集。

- 本地振荡器:用作频谱搬移过程中的载波信号,将射频域的信号下变频到基带。

- 混频器:频谱搬移过程中等价于乘法器的元件,但由于本振输入端存在

发射板

发送子板可以实现已调信号的上变频发送,在本设计中将采用低中频架构实现功能。一个经典的发射机架构包括有:滤波器、混频器、本振、射频滤波器、功放、天线。经典的模拟链路框图如图2-6所示,图中上半部分描述了无线电接收机部分,下半部分描述了无线电发射机部分。

在上图所示的模拟链路设计中,本设计主要涉及如下部分:

- 滤波器:该部分紧跟已调信号的输出端,用于滤除模拟信号中的谐波与噪声信号。

- 混频器:用于信号上变频,与接收板中混频器的作用恰好相反。

- 本振:充当上变频过程中的载波信号,用于实现信号的频谱搬移。

- 功放:用以将射频小信号进行放大,进而实现在无线空间中的长距离传输。在实际应用中功放工作在丙类工作状态,借助较小的导通角实现较高的功率与效率。

- 射频滤波器:由于本振的多次谐波特性与混频器的整流特性,使得经过上变频的射频信号拥有较多的谐波特性。这些谐波会作为杂散去污染无线电频谱,同时也会降低系统的信噪比,因此在实际应用中常常会在功放后添加一级射频滤波器。

核心板

核心板主要用于信号采集、解调、调制与信号产生,同时还包含简单的人机交互界面与调试接口。

- 主控芯片:主控作为整个系统的核心所在,承担着数字信号与交互逻辑的处理。主控芯片的外围电路设计需要拥有较强的可靠性与可调试性,因此在进行结构设计时就需要为电源与时钟预留充足的冗余,对于调试接口也要尽可能多地引出。

- 信号调理:信号调理的对象主要包含四种:接收板发送到主控的IQ信号、主控发送到发射板的调制信号、解调后的模拟信号以及原始模拟信号。信号调理主要进行的工作大致包括滤波、放大、衰减与幅度调整,进而完整地发挥出ADC与DAC的全部性能,提高整个系统的动态范围与信噪比。

- 人机交互:人机交互部分主要分为参数的接收与显示,进而实现操作者对解调后信号的接收与相关参数调整的功能。对于解调后为模拟信号的信号路径,操作者观察解调信号的途径转换为调理后运放以及功放输出的模拟信号。

元件选型

基带调制解调器

该设计的目的是为了支撑通信相关专业的教学实验,基带带宽要求一般较低,同时受限于开发与物料成本因素在此不考虑FPGA+独立转换器方案。下文将会对资源占用情况进行评估,并提出几种较为合适的应用方案。

- Xilinx 7系全系集成1M的XADC,因为大量供货的原因,XC7Z010CLG400-1的全新价格在100元附近。

- 安路科技EG4S20BG256,内置1M ADC与2M*32Bits的SDRAM,零售报价60元左右。其中EG4S20BG256的LUT数约为20K,与ZYNQ7010资源数相当。

- STM32F4系列,带FFU运算单元与ARM官方DSP库支持。本设计要求带多路ADC与DAC,在保证成本够低的情况下RAM尽可能地大,在此选用F407/417或F405/415系列。

综合开发与物料成本,最终选定STM32F405RGT6 MCU进行平台的开发。该芯片为LQFP-64封装,零售报价30元。其也拥有国产二进制兼容方案:GD32F405RGT6,在避免断货的情况下进一步下探零售报价到20元。

本振

本振作为信号的载波,在混频器中与基带信号相乘,对其的要求为低噪声、高稳定度与较好的低频特性。待选方案有MCU产生、晶振提供、直接数字频率合成器与锁相环。

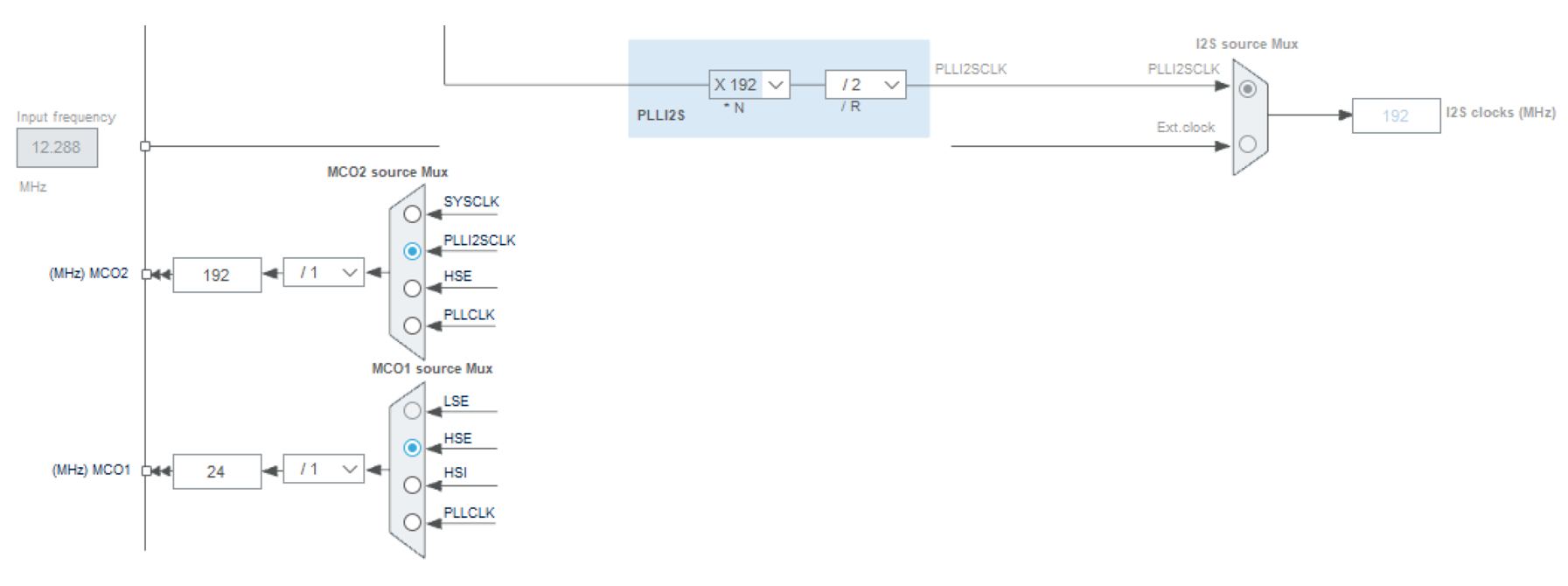

MCU产生:该方案使用STM32内置的Master Clock Output输出频率,一般用作时钟使用。其中MCO2的输出由PLLI2S输出,无需额外添加元件,但存在频率精度不高(1MHz)、频率稳定度较低的特性。不太合适频率较高和颗粒度较低的本振产生,但可作为MSi001的参考时钟使用。

- 晶振提供:晶振分为有源晶振与无源晶振,其中无源晶振输出正弦波,有源晶振内置整形电路输出波形为方波。若使用晶振作为本振其成本较低,但存在以下问题:1、晶振的触发电平较高,会使混频器饱和,需额外添加衰减器。2、晶振存在泛音,需添加滤波电路。3、本振频率固定,更改频点就需要更换晶振。

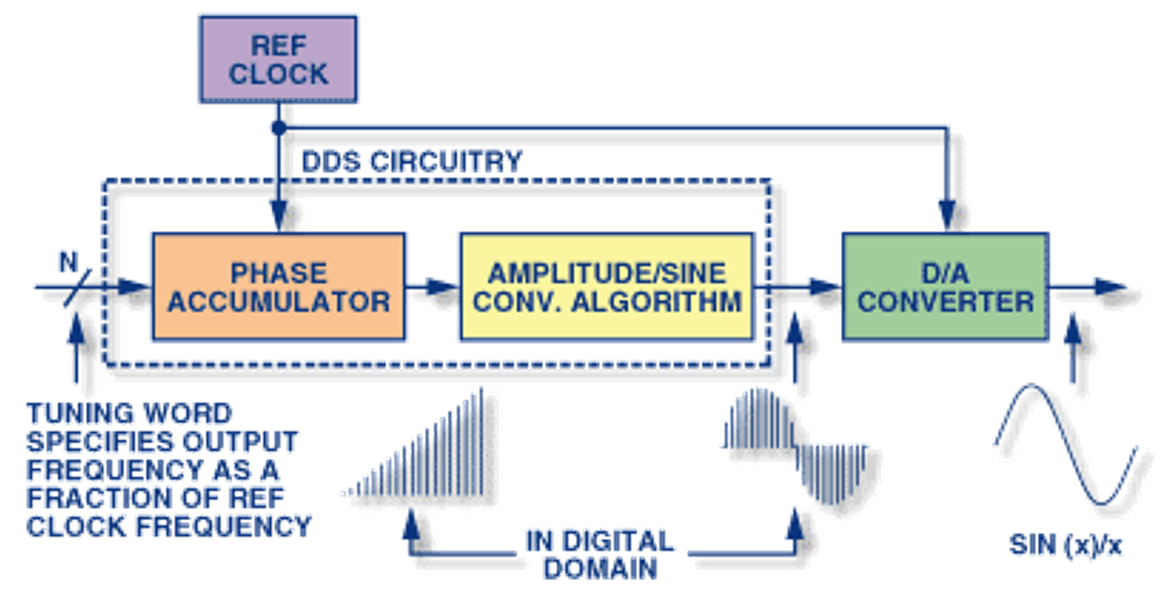

直接数字频率合成:DDS的内部由控制器、查找表与高速DAC构成,其本质上仍使用高速DAC产生单频载波。如需达到500M的频率范围,要求DDS的时钟频率与DAC工作频率至少达到1G,成本极高。但因为DDS的相位、频率与幅度可以突变,使之在ASK、FSK、PSK调制等方面有较多的应用。图2-8描述了一个典型的DDS系统,其由参考源、相位累加器、幅度变换器与DAC共同组成。

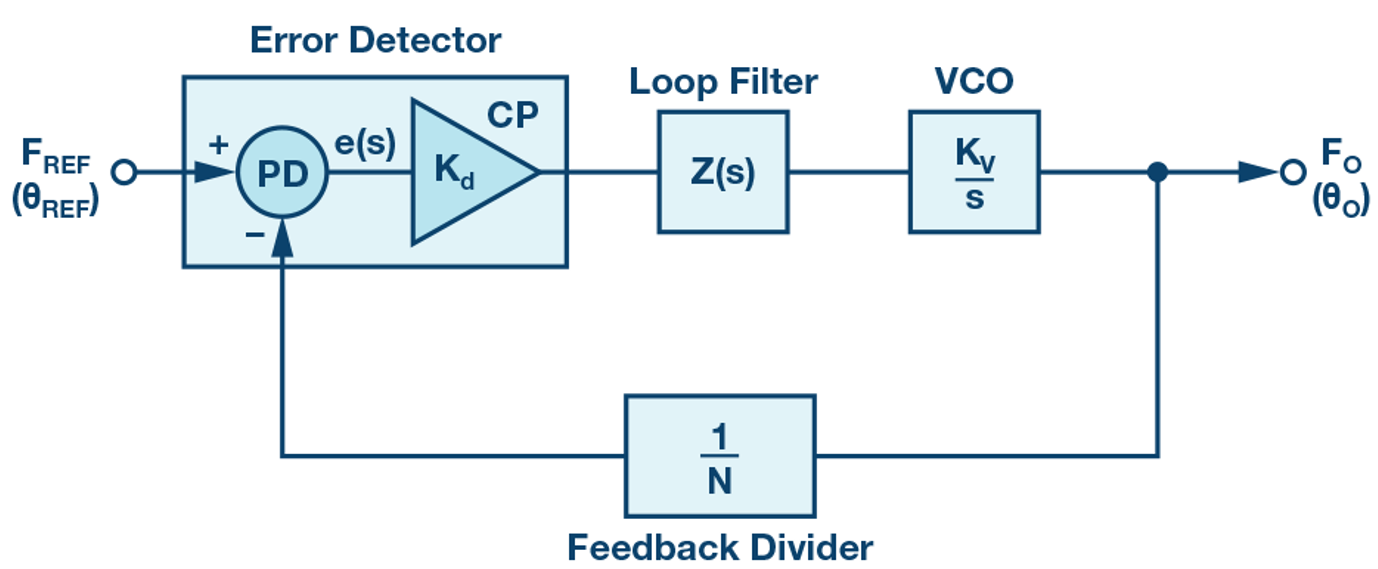

锁相环:锁相环有着杂散低、频率范围广与成本低的特点,虽其无法实现频率的突变,但用作本振已经足够,因此在本设计中使用其作为本振并通过MCU进行控制。一个典型的PLL系统如图2-9所示,其由鉴相器、环路滤波器、VCO、分频器共同组成。

考虑开发成本与调试周期,使用内置VCO的时钟产生芯片Si5351作为本振,使用该方案时需外加衰减器与滤波器,用以避免本振输入到后级混频器造成的非线性饱和。

混频器

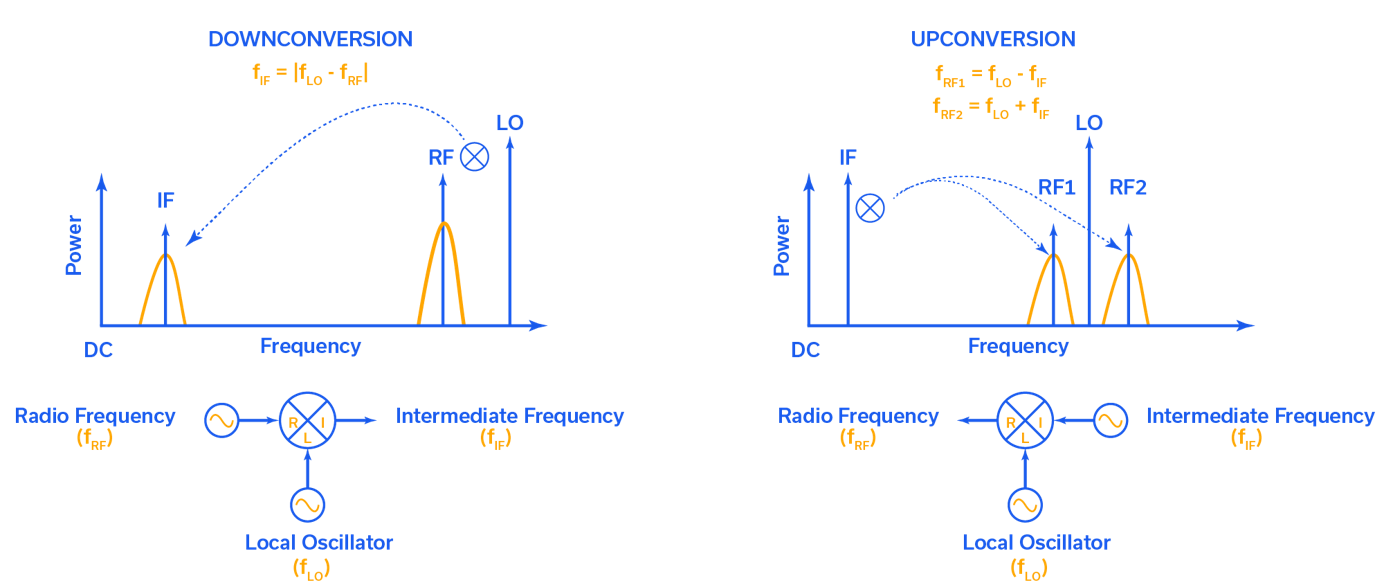

信号通路上器件的选型,除了频率范围的考虑,还应加入噪声系数(插入损耗)、输入功率等指标。待选的混频器类型有乘法器、无源混频器、IQ镜像抑制混频器与有源混频器。一个典型的混频器实现的功能是频谱的搬移,即将频率由IF搬移到LO附近,上下混频的频谱示意图如图2-10所示。

- 乘法器:混频器的本质上是利用乘法器对LO与IF频率的积化和差,经过乘法器运算后的频率包含和频、差频。但是一般而言乘法器拥有更高的线性度,而混频器则会对输入进行整形。但乘法器的高线性度在混频应用时会造成负面的影响,载波上噪声带来的无用幅度信息会被加到乘法计算中,造成输出混频结果的噪声叠加。

- 无源混频器:无源混频器的所有部分都由无源器件构成,无需额外供电。无源混频器的典型特点是噪声系数小、频率范围广与线性度高,故其在很多要求较高的领域有较为广泛的应用。但是因为无源驱动混频器常常使用对称的二极管作为关键结构,因此需要高达13~20dBm的LO驱动。此外,较高的LO功率会导致本振在输出上的频率耦合。

- IQ镜像抑制混频器:镜像抑制混频器相较于传统的无源混频器拥有较好的镜像抑制特性,其通过一个90°相移器对输入的LO进行希尔伯特变换后再分别于IF相乘,最后相加或相减得到上下边带。对于上变频器一般称作IRB,对于下变频器一般称作SSB。与前文的无源混频器需要大功率LO特点类似,因为功分器的加入,镜像抑制混频器的输入功率往往还要再高3dB。因为高度有效的镜像抑制特性,使得其不需要再进行后端滤波,节省了需许多成本。

- 有源混频器:有源滤波器与无源滤波器的最大区别是输入端的放大器,在有源滤波器中一般会加入放大器以实现较低的输入驱动功率。除此之外,有源混频器一般还会集成倍频器以达到更高的频率。但是,因为有源器件的引入,使得有源混频器的噪声系数与线性度对有所降低。

基带由STM32内置外设产生,混频器在此选用有源混频器SA612以满足低频段需求。

调谐器

分立元件组成的LNA、本振、混频等电路若使用分立元件搭建,一般具有较大的离散性与随机性,在此考虑使用集成调谐器替代接收机中LNA->ADC的全部过程。同时单片集成调谐器能够极大地克服零中频架构中的直流偏置与IQ不平衡。对调谐器的选型要求为宽频带、低中频带宽与低成本。

MSI001

为SDRPlay RSP1采用的方案,零中频模式带宽为200KHz,调谐器的频率范围150KHz~1.7GHz(在RSP1的应用上频率范围扩展到了1KHz~2GHz)。该芯片最初被设计用于DVB-T、ISDB-T、DRM、FM与AM信号的接收,其在极宽的频率范围内拥有零中频与低中频两种工作模式,并且针对每个频段进行了频率特性优化。

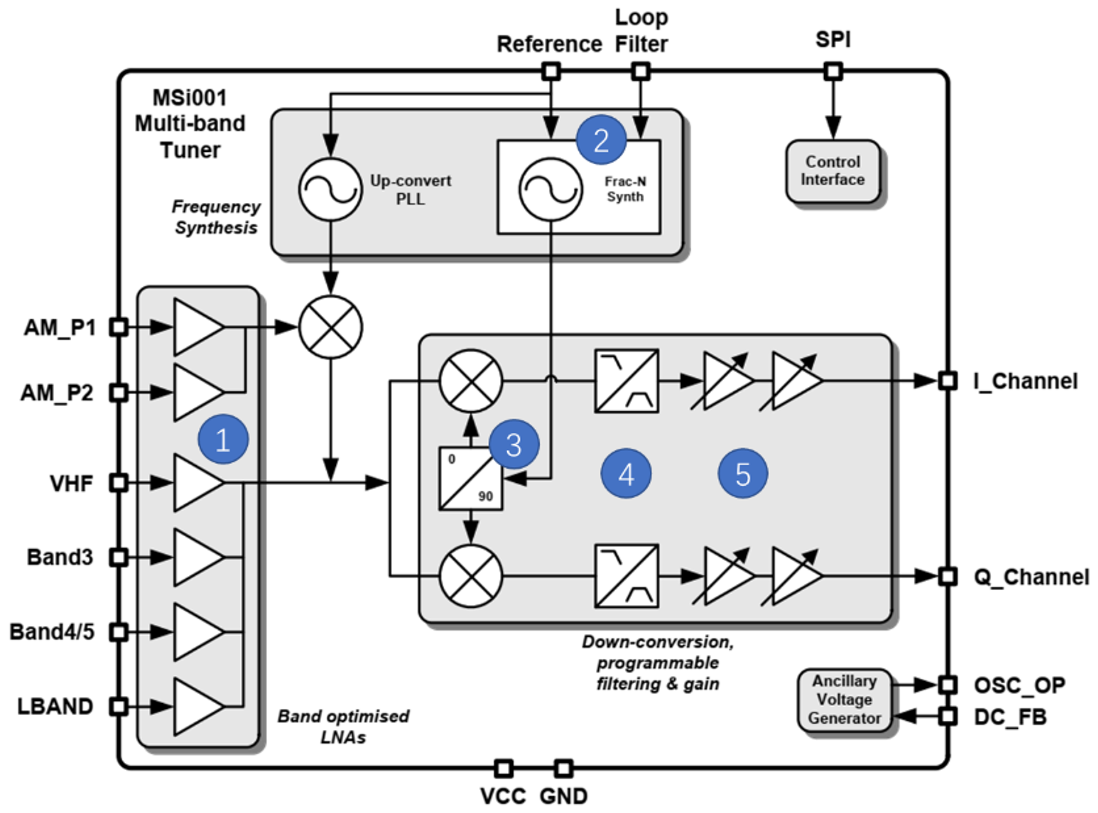

该芯片的内部框图如图2-11所示,图中标号①为低噪声放大器;标号②为锁相环本振源;标号③为希尔伯特变换器,用于将信号进行移相以得到正交IQ信号;标号④为中频滤波器,用以将杂散信号滤除;标号⑤为中频放大器,将滤波后的小信号放大到ADC的量程范围内。

R820T

为RTL-SDR电视棒采用的方案,最开始是被用作DVB-T解调的器件。频率范围42MHz~1002MHz,缺少AM频段的支持。同时其工作模式为低中频调谐器,需进行正交化并要求较高的ADC与DSP速率,暂不考虑。

RDA5815

为DVB-T电视棒常用的方案。频率范围250MHz~2150MHz,为零中频调谐器,但缺少低频频段支持,暂不考虑。

交互

调制信号经过解调后得到基带信号,故在此要求对解调后基带信号进行输出。当解调基带信号为数字信号时,以数字形式展示;当解调基带信号为模拟信号时,以模拟形式展示。此外,还应当进行原始基带信号的采集,并配备若干按键,用于参数的调整或选择。

数字信号

采用OLED 12864显示屏进行解调参数的显示与基带的数字化输出,小尺寸OLED相较于LCD拥有成本低与显示效果好的优点。同时在该模块上还可以显示参数信息,并通过按键进行模式选择与调整。

模拟信号

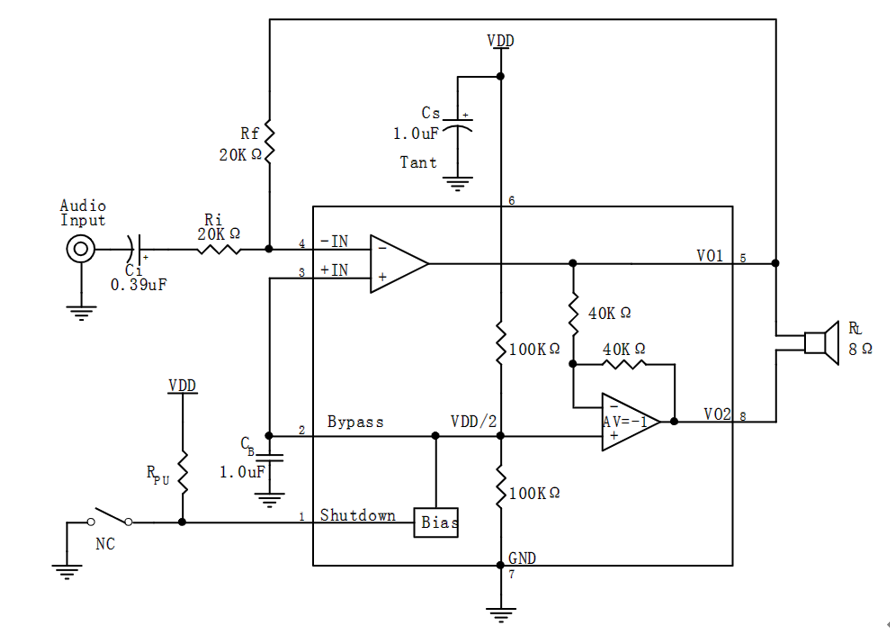

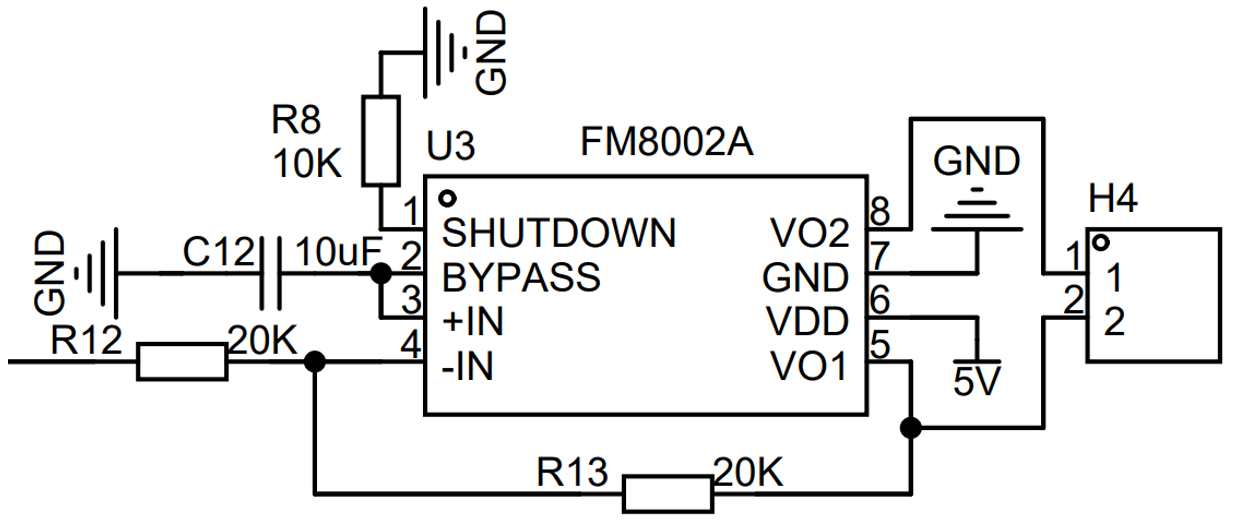

AM、FM等模拟调制信号的基带信号常为模拟信号,要求信号解调后能够正常输出原始波形。在实际生活中,基带信号常为音频信号,故将其通过功放电路送入扬声器后即可实现播放,在此处采用常见的FM8002A功放实现。

基带信号

本设计包含对基带信号的调制,由于原始基带信号多为模拟信号,因此在处理时需要通过DAC进行数据的转换。由于整板的主电源轨为3.3V,因此模拟前端的调理电路需要使用低电压运放,在此采用经典运放LM358的低电压版本LM358V。

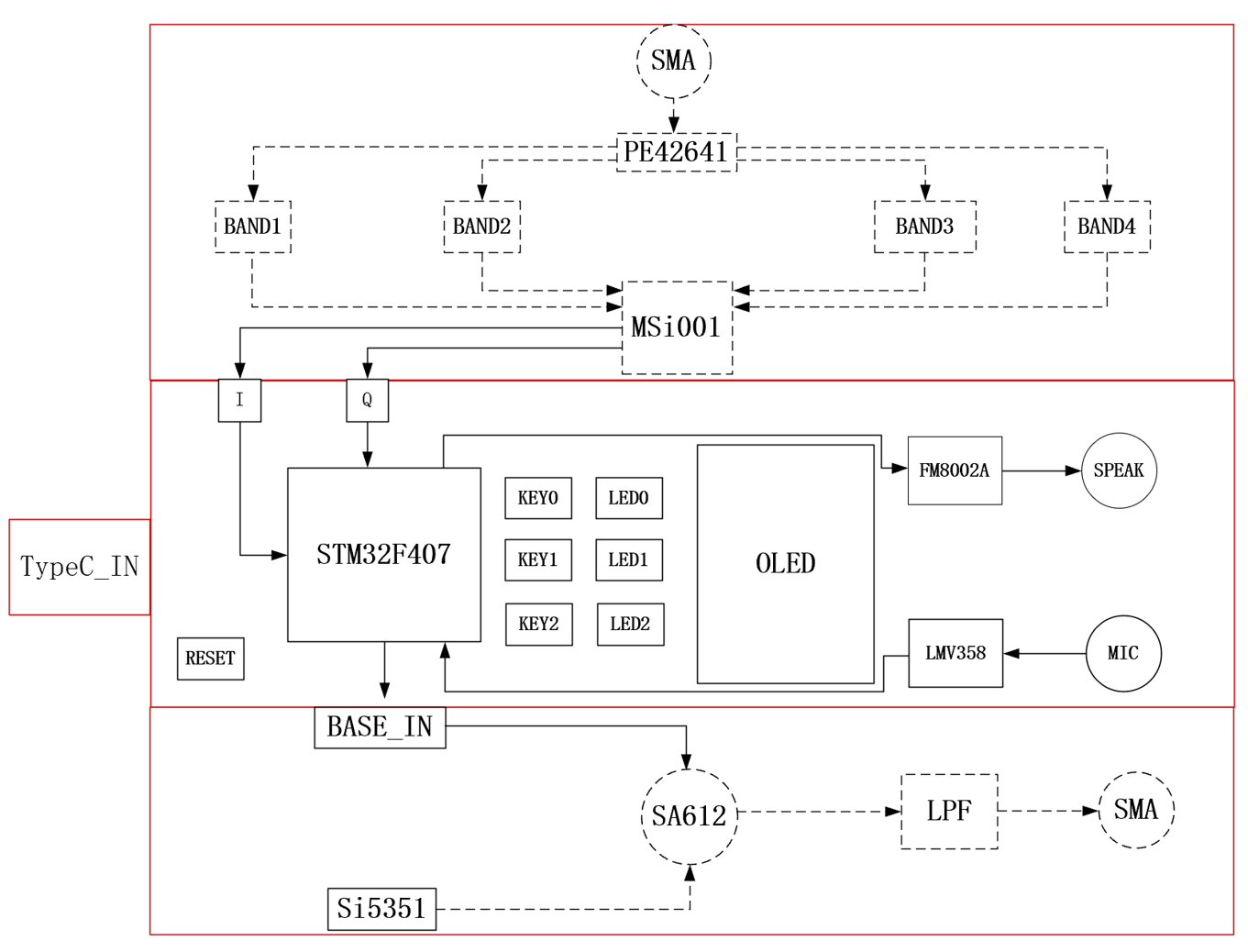

根据本节对架构与元件的选型与对比,最终得出本设计的完整信号流图。完整信号流图如图2-12所示,其中各个子模块通过框图线区分,从上到下依次为接收板、核心板与发射板。系统设计中所使用到的器件均展示在该框图中,其中PE42641为射频开关、MSi001为调谐器、STM32F407为MCU、FM8002A为功率放大器、LMV358为运算放大器、SA612为混频器、Si5351为本振。

3、硬件设计

射频电路的设计开发流程中有许多需要注意的问题,当系统工作频率不断升高时,电路上一些元件就开始出现非理想特性,进而造成串扰与无效耗散。因此,我们对高速电路的设计进行特殊考虑的目的就是为了在电路设计、叠层选择与布局布线时,尽可能地将非理想特性纳入考虑范围。同时,低速与数字部分的设计虽然要求不高,但也有一些不容忽视的问题所在。

本章节的内容主要包括滤波器设计、阻抗匹配、信号屏蔽与信号调理。设计所需的EDA工具为立创EDA专业版,滤波器设计工具为RF-Tools,阻抗计算工具为Si9000,电路仿真工具为LTspice。所有设计会在后文的“测试验证”环节通过仪器进行实测,并进行简要评估。

滤波器设计

由于自由空间中的频谱被各种各样的无线信号所填充,因此要想在其中选出有用的信号就必须滤除其它频段的无用信号。否则其他频段的信号在下变频时映射到基带的同时,也会造成前端LNA的过载减小系统动态范围。

射频系统中的滤波器分为两种,即有源滤波器与无源滤波器。其中有源滤波器使用运算放大器作为关键器件,无源滤波器则使用RLC元件作为全部元件。前者往往能拥有一定的信号增益,但同时会引入噪声信号且最高频率不高。后者由于完全使用无源器件搭建,因此能够实现非常好的频率响应。

射频前端滤波器

该部分的滤波器位于调谐器前端,用于在信号接收时滤除其他频段的干扰信号。例如在接收AM信号时,将功率较大的FM信号滤除,可以极大地提高系统动态范围。如前文在结构划分中所描述的那样,常用的无源模拟滤波器分为:巴特沃斯滤波器、切比雪夫滤波器、椭圆滤波器与贝塞尔滤波器。

在前端滤波器选型时,我们对带内信号的要求的是尽可能地平坦,用以满足在该频段下的模拟前端参数与基带信号一致性,使得在后续过程中只需要针对各个频段而非频点做校准。对于带外信号的衰减,我们不要求过于陡峭的特性,只需要能将该频段的信号进行压制避免LNA过载即可。因此,我们将会选用Butterworth滤波器进行射频模拟前端滤波器的设计。我们将会首先通过RF Tools进行软件辅助设计,出于元件误差容限的原因,再通过LTspice进行元件数值微调。

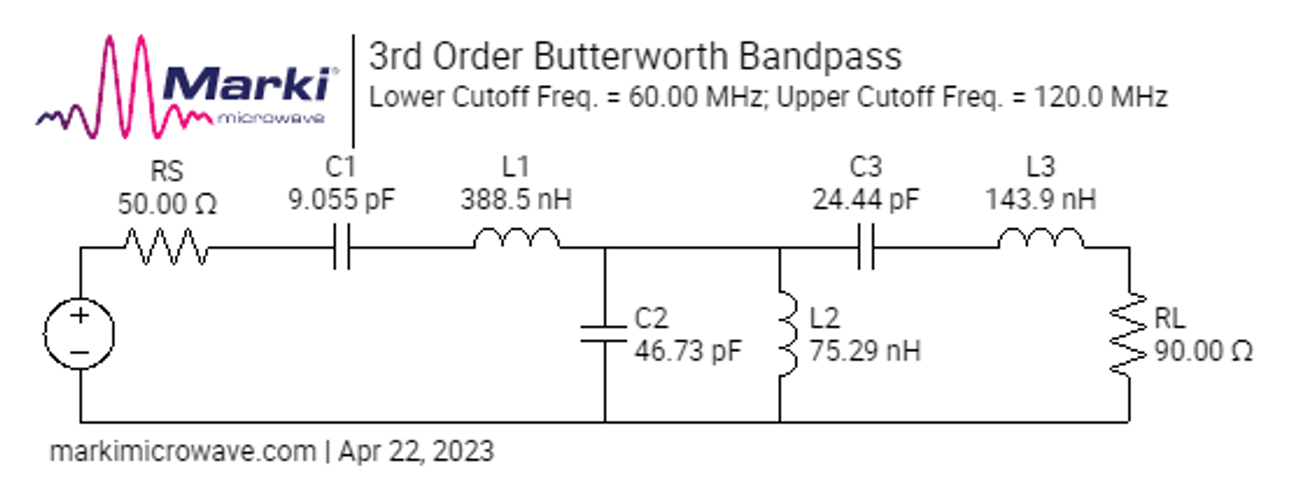

完整的计算机辅助设计流程大致分为如下步骤:确定滤波器类型、上下限截止频率、通带波动、阻带衰减、阶数、输入阻抗、输出阻抗。如前文所述,本设计的滤波器类型选用Butterworth型,通带波动<1dB,阻带衰减>40dB,输入信号接天线固定为50Ω,输出阻抗取决于所用MSi001频段模拟输入特性。对于经典的无线电环境,滤波器的主要用途是滤除开放频段的无线电信号,常见有AM、FM、433M频段的强干扰信号。因此截止频率可以围绕上述信号的频率上下限与MSi001的输入频段进行设计,在此选用四个频段:0-60MHz、60-120MHz、120-400MHz、400-1000MHz,下文的流程主要以60-120MHz为例。

RF-Tools辅助设计

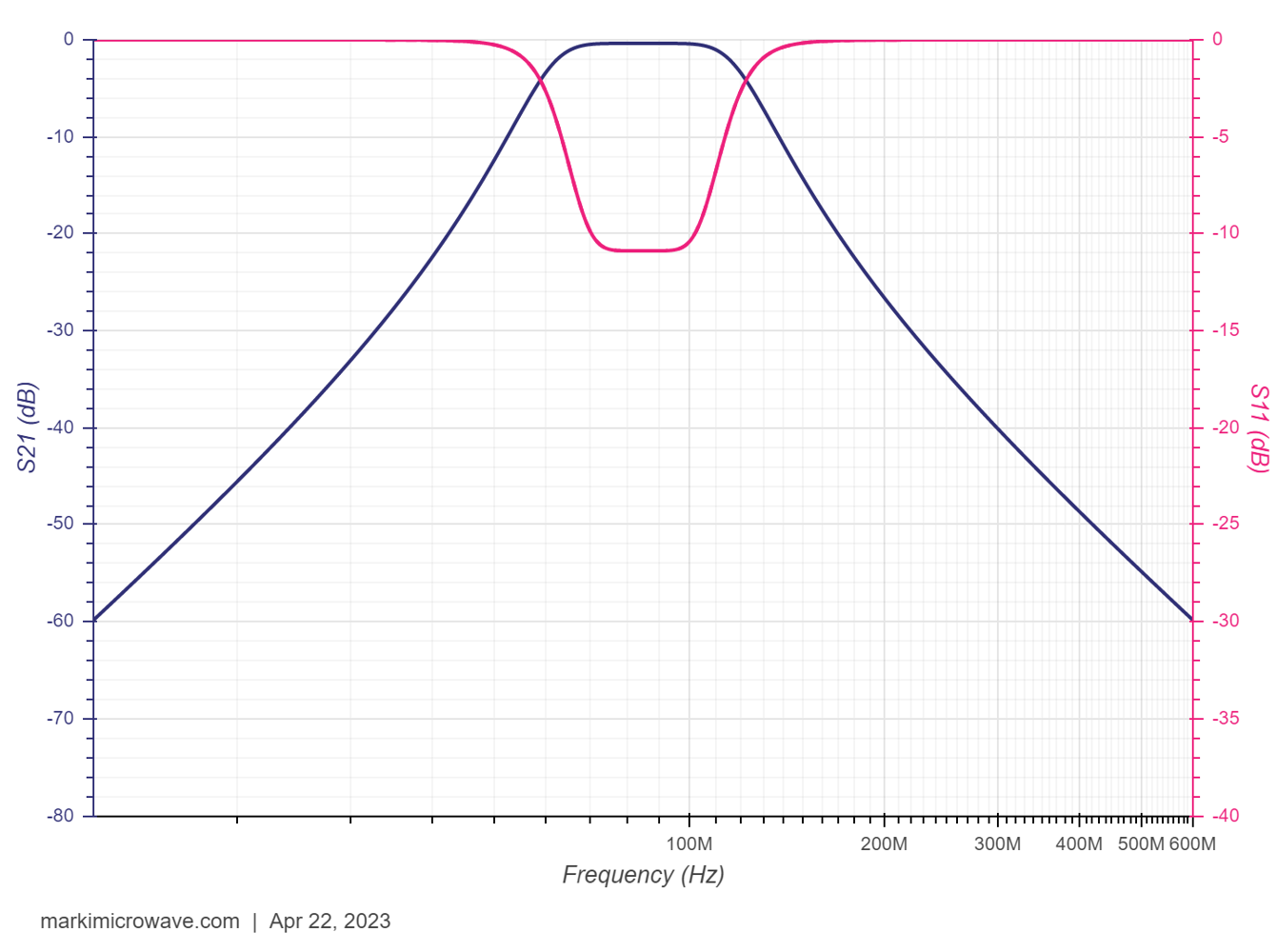

使用RF-Tools进行滤波器的在线设计,输入需求为带通滤波器、巴特沃斯型、3阶、上限截止频率120MHz、下限截止频率60MHz、输入阻抗50Ω、输出阻抗90Ω,点击计算便可由计算机自动生成所需滤波器。图3-1为工具自动生成的理想RLC数值下的滤波器电路图,然而在实际工程实现中无法找到对应数值的元件,所以下一步便是将其导出到LTspice并根据库存元件进行修改并仿真幅频响应。

工具同时给出了理想状态下的插入损耗(S21)与回波损耗(S11),从图中我们可以很明显地看出滤波器的带通特性,通过光标测量上下限截至频率也与理论设计相符。

LTSpice微调

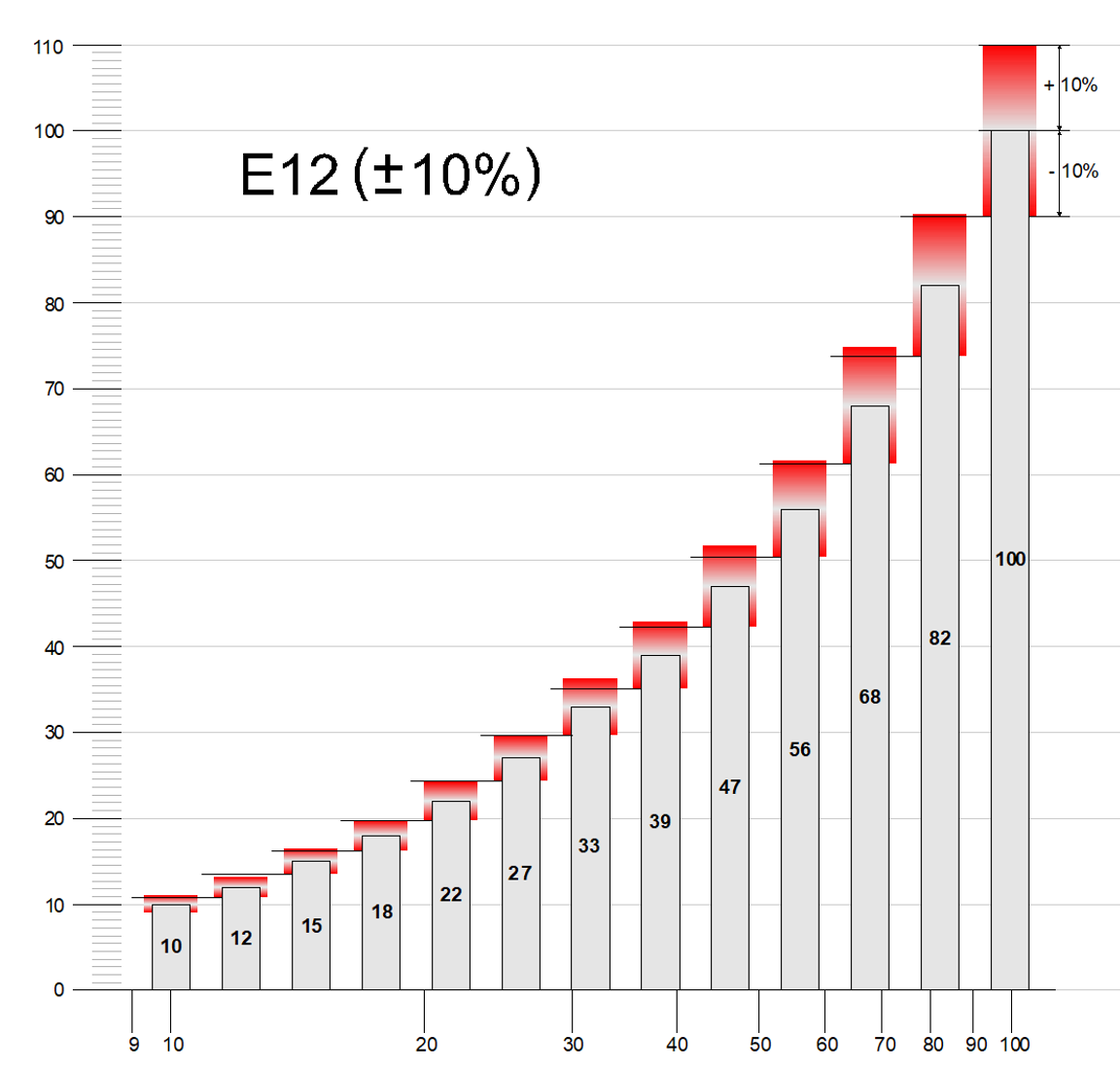

显然,我们无法取得理论电路中RLC数值的元件,必须要根据库存情况进行微调。在实际工业生产中,为了避免物料浪费引入了E系列作为RLC数值划定的标准。譬如对于E12而言,其定义为在[1,10)的范围内取出恰当的12个数值,使得所有数字拥有确定的比例范围。常见的数值系列分为E6、E12、E24、E48、E96与E192,精度从20%提高到0.5%。下图3-3表述E12系列内的取值,可以观察到其与理想数值之间的误差都在10%以内。

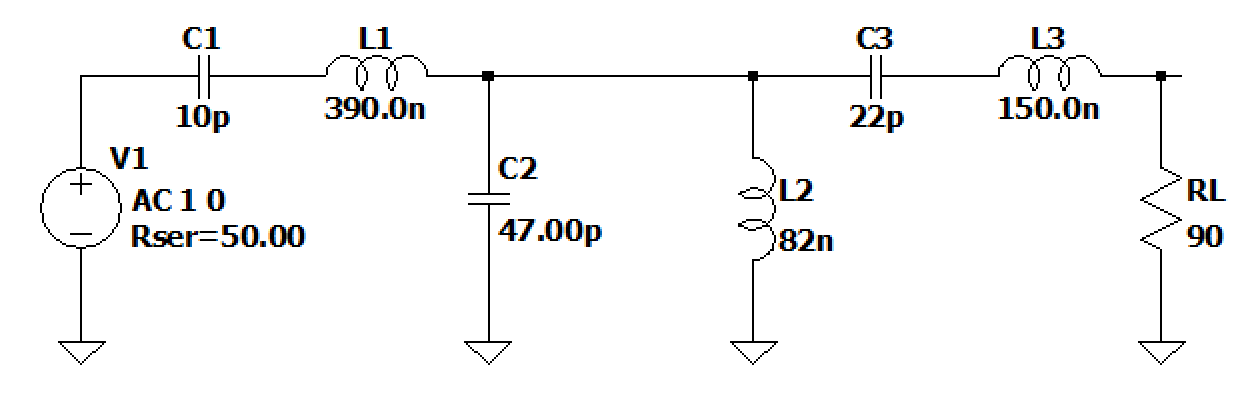

在滤波器设计的元件选型中常常采用1%精度的RLC,同时根据库存物料修改电路如图3-4所示。

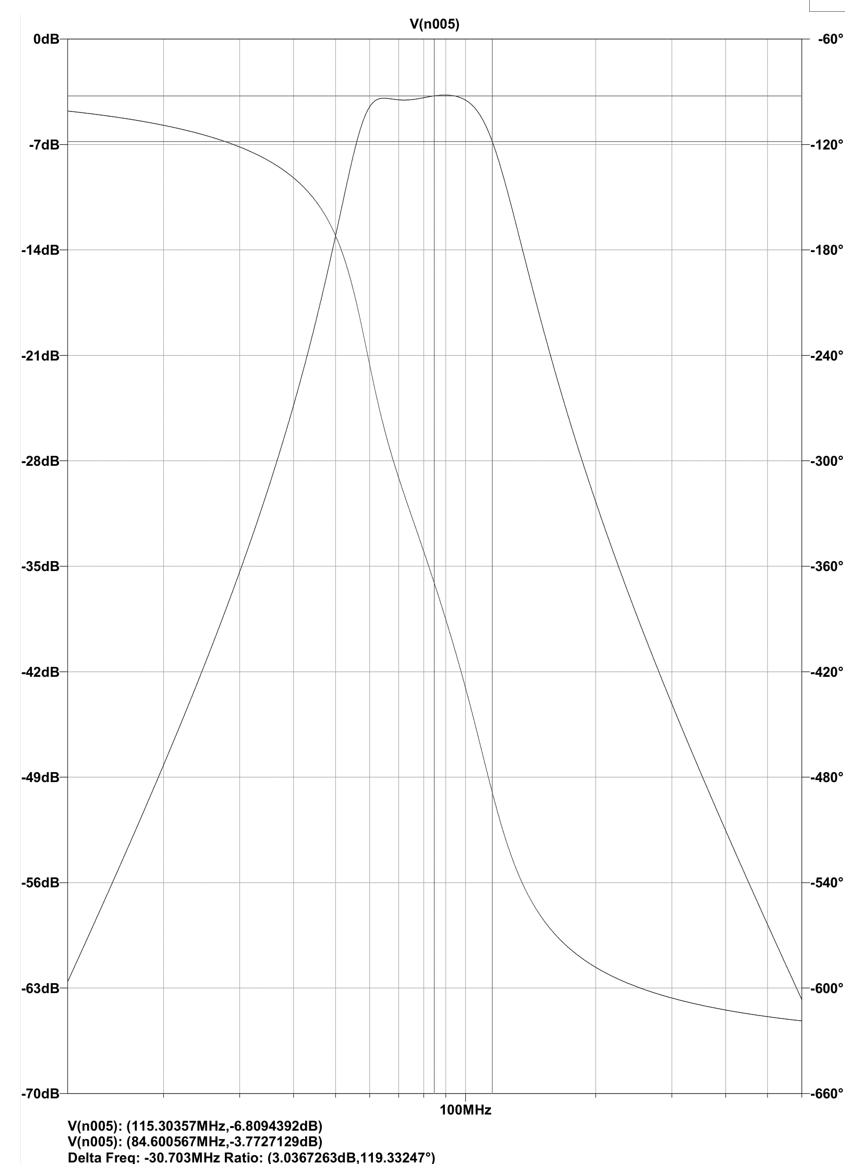

修改后进行交流仿真,指定扫频点数1000点、扫频方式十倍频,起始频率为12MHz,终止频率为600MHz。实际测量到的通带频率为56MHz-115MHz,通带波动296mdB,满足设计要求。

抗混叠滤波器

抗混叠滤波器主要用于ADC的采样前端,用于滤除带宽以外的信号,避免噪声被映射到带内造成混叠现象。根据奈奎斯特采样定理可知,采样率$f_s$与信号最高频率$f_H$的关系需要满足$f_s>=2*f_H$,具体表述推导如下。下式中$s(t)$表示采样脉冲,$T_s$表示采样周期,$\mathcal{F}[s(t)]$表示采样脉冲的频域表示,可以看出采样脉冲在时域上表现为周期性脉冲,频域上则表现为冲激函数的周期序列。

$$ \begin{gathered} s(t)=\sum_{k=-\infty}^{+\infty} \delta\left(t-k T_s\right) \\ \mathcal{F}[s(t)]=\frac{1}{T_s} \sum_{n=-\infty}^{+\infty} \delta\left(w-n w_s\right) \end{gathered} $$

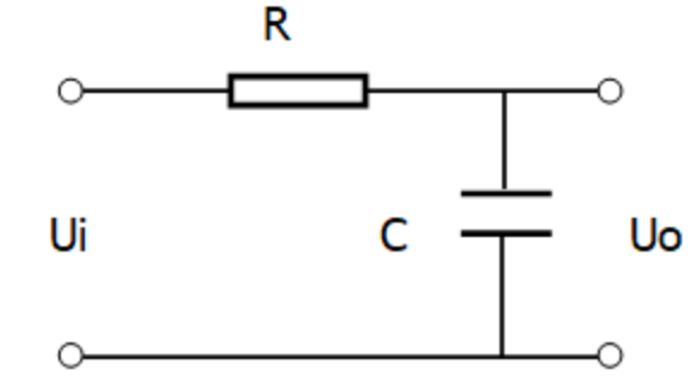

故经过采样后的信号在频域上表现为基带信号的周期延拓,要想保证基带信号在延拓后不被干扰,及必须保证频域上的延拓周期大于2倍信号周期,即采样率频率大于等于2倍信号最高频率。因此要想正确地采样模拟信号,就必须在ADC采样前就进行带宽限制,滤波器会将其限制到$f_s/2$的 频率范围内,出于工程实现的需要,往往滤波器截止频率会略低于该值。在ADC采样前进行带宽限制避免混叠的滤波器,我们常称之为抗混叠滤波器,低频段范围内的抗混叠滤波器常常采用一阶RC低通滤波器。譬如在ADC1、ADC2与ADC3的输入通道上都各自连接有一个低通滤波器,用于对带外信号的滤除,提高信噪比。RC低通滤波器的结构非常简单,由一颗电阻与一颗电容组成,截止频率由$f_c=1/{2\pi RC}$计算而得,具体推导如下所示。图3-6描述了一个典型的RC一阶低通滤波器的电路示意图,图中$U_i$表示输入电压、$U_o$表示输出电压、$R$表示电阻阻值、$C$表示电容容值。

可以推导出输入输出电压下的传递函数$H(j \omega)$,如下式所示。

$$ H(j \omega)=\frac{U_O}{U_i}=\frac{X_c}{R+X_c}=\frac{\frac{1}{j \omega c}}{R+\frac{1}{j \omega c}}=\frac{1}{1+j \omega R C} $$

计算该复数的模值,如下式所示。

$$ |H(j \omega)|=\sqrt{\frac{1}{1+(\omega R C)^2}} $$

当电压增益下降为原始的$\frac{\sqrt2}{2}$倍时,此时的频率定义为截至频率$f_c$,取得该数值时$f_c=\frac{1}{2\pi RC}$。

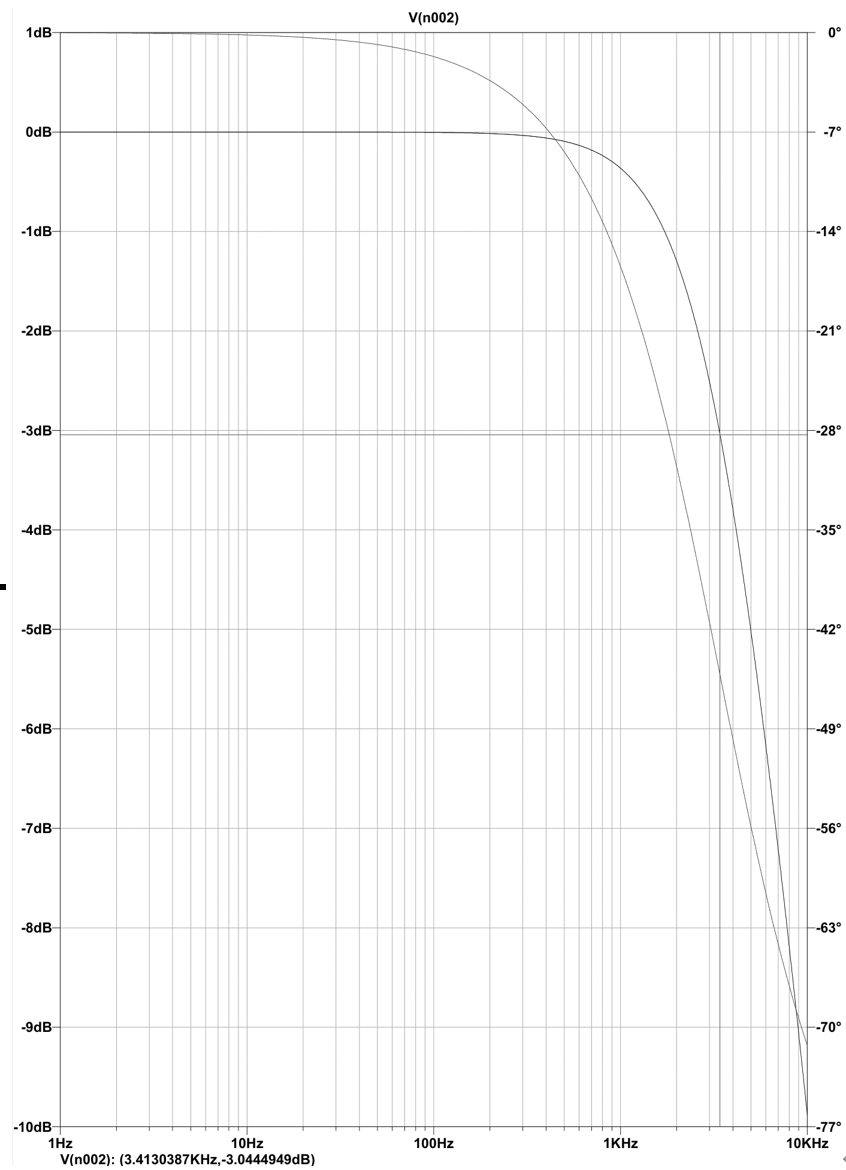

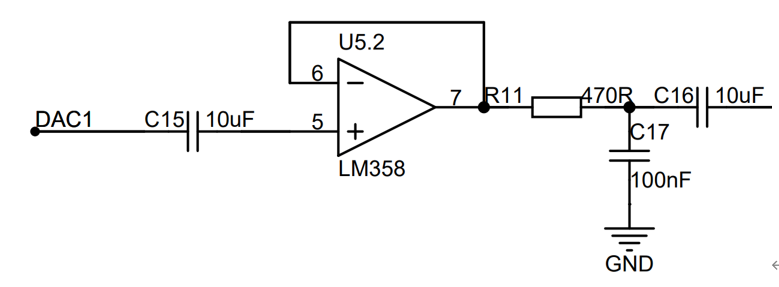

举例介绍ADC3的前端抗混叠滤波器设计流程,其它路径上的滤波器设计步骤与该路径相似不做赘述。RC低通滤波器的设计与仿真需要综合考虑前后级电路的特性,信号截至频率与衰减速度。对于理想的前后级电路(前级输出阻抗无限小,后级输出阻抗无限大),无需考虑阻抗因素,直接使用$f_c=\frac{1}{2\pi RC}$计算即可。阻带衰减速度的设计考虑则主要涉及到带外大信号的幅值,一般 -20dB / Dec足够使用,如需更快速的阻带衰减则可以考虑使用多阶RC滤波器。在本设计中ADC3主要用于采集模拟基带信号用于调制,该信号主要为0-3.4KHz范围内的音频信号。故根据奈奎斯特采样定理可以确定ADC采样率的最低数值,在此选用10KHz。RC模拟抗混叠滤波器的前端带宽选用3.4KHz,考虑器件误差在此选用$R=470\Omega,C=100nF$作为滤波器的参数,截止频率计算为: $f_c=\frac{1}{2\pi RC}=3386Hz$。仿真测试结果如图3-7所示,符合设计要求。

阻抗匹配

由于射频电路的频率极高,使得原本理想的集总电路电路系统变成了分布参数电路系统。在该系统中射频电路的源、负载、传输线在设计时候就需要进行匹配,不恰当的会造成信号的耗损与反射。常规定有反射系数$\Gamma(z)$,定义为传输线上任意一点的反射波电压与入射波电压之比,定义如下式所示。

$$ \Gamma(z)=\frac{U_r(z)}{U_i(z)} $$

对于无损传输线$\gamma=j\beta$,规定输入源阻抗$Z_S$,终端负载阻抗$Z_L$。则有源端电压反射系数$\Gamma(S)$与负载端电源反射系数$\Gamma(L)$,具体关系如下式所示。

$$ \begin{gathered} \Gamma(z)=\frac{A_2 \mathrm{e}^{-\mathrm{j} \beta z}}{A_1 \mathrm{e}^{\mathrm{j} \beta z}}=\frac{Z_L-Z_O}{Z_L+Z_O} \mathrm{e}^{-\mathrm{j} 2 \beta z} \\ \Gamma_S=\frac{Z_S-Z_O}{Z_S+Z_O} \\ \Gamma_L=\frac{Z_L-Z_O}{Z_L+Z_O} \end{gathered} $$

因此为了使射频信号在传输的过程中无反射,要求对微带传输线进行阻抗匹配,则有$Z_s=Z_o=Z_L$。在典型的射频系统中,该阻抗数值为50欧姆。对于源端与负载端的匹配,在芯片设计时已经由厂商做好,对于不是50Ω的非标准系统则需要使用电阻或者LC电路进行额外匹配。因此在常见的射频电路设计过程中,传输线的阻抗匹配就显得尤为重要,一个良好的匹配系统能将信号以最大功率由源端传输到负载端。典型的传输线分为微带线与共面波导,在PCB设计的过程中出于板材叠层的原因,前者常用于多层板设计,后者常用于单/双层板设计。

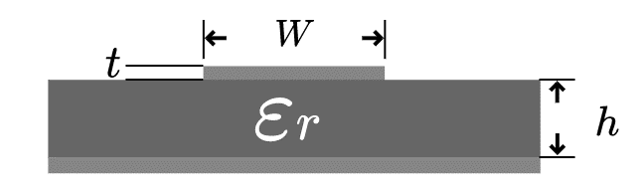

多层板阻抗匹配

由于多层板(>=4层)可以自定义叠层设计,所以可以在第二层引入地层负片作为参考地平面。一个典型的微带线示意图如下图所示,其中$W$表示传输线宽度、$t$表示传输线高度、$h$表示传输线到参考地平面距离、$\omega_r$表示介质的介电常数。

对于该微带线模型,其阻抗$Z_0$的计算公式可以表述为下式。

$$ Z_o=\frac{87}{\sqrt{\varepsilon_r+1.41}} \times \ln \left(\frac{5.98 h}{(0.8 w+t)}\right) $$

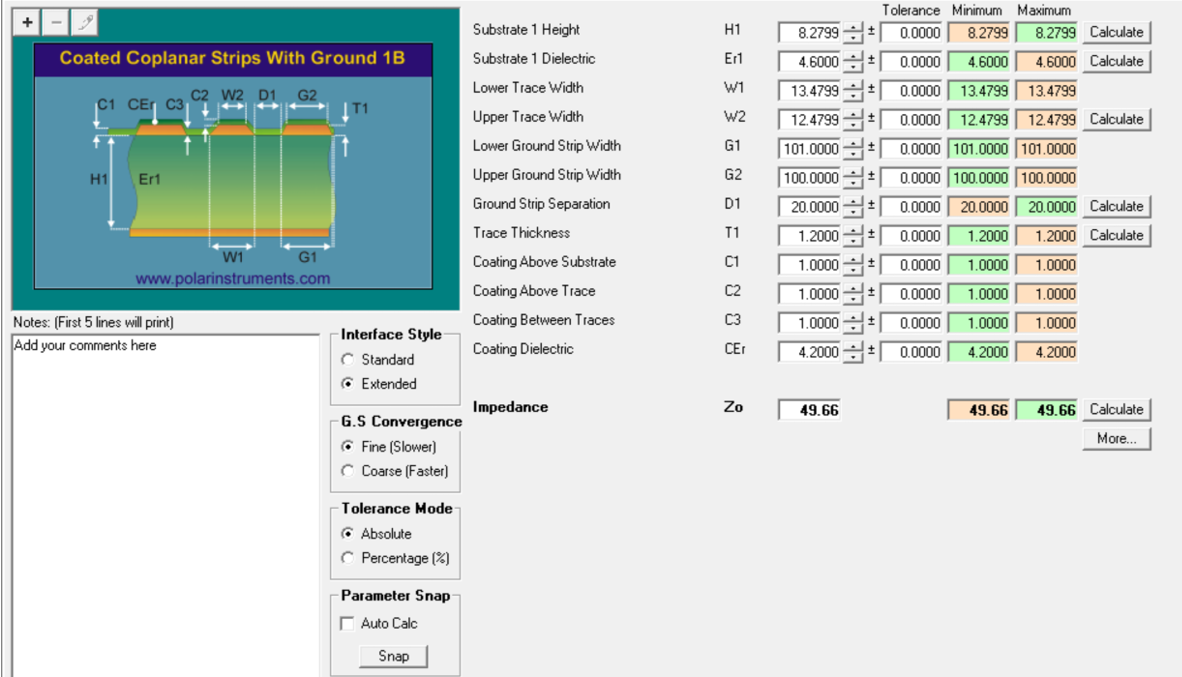

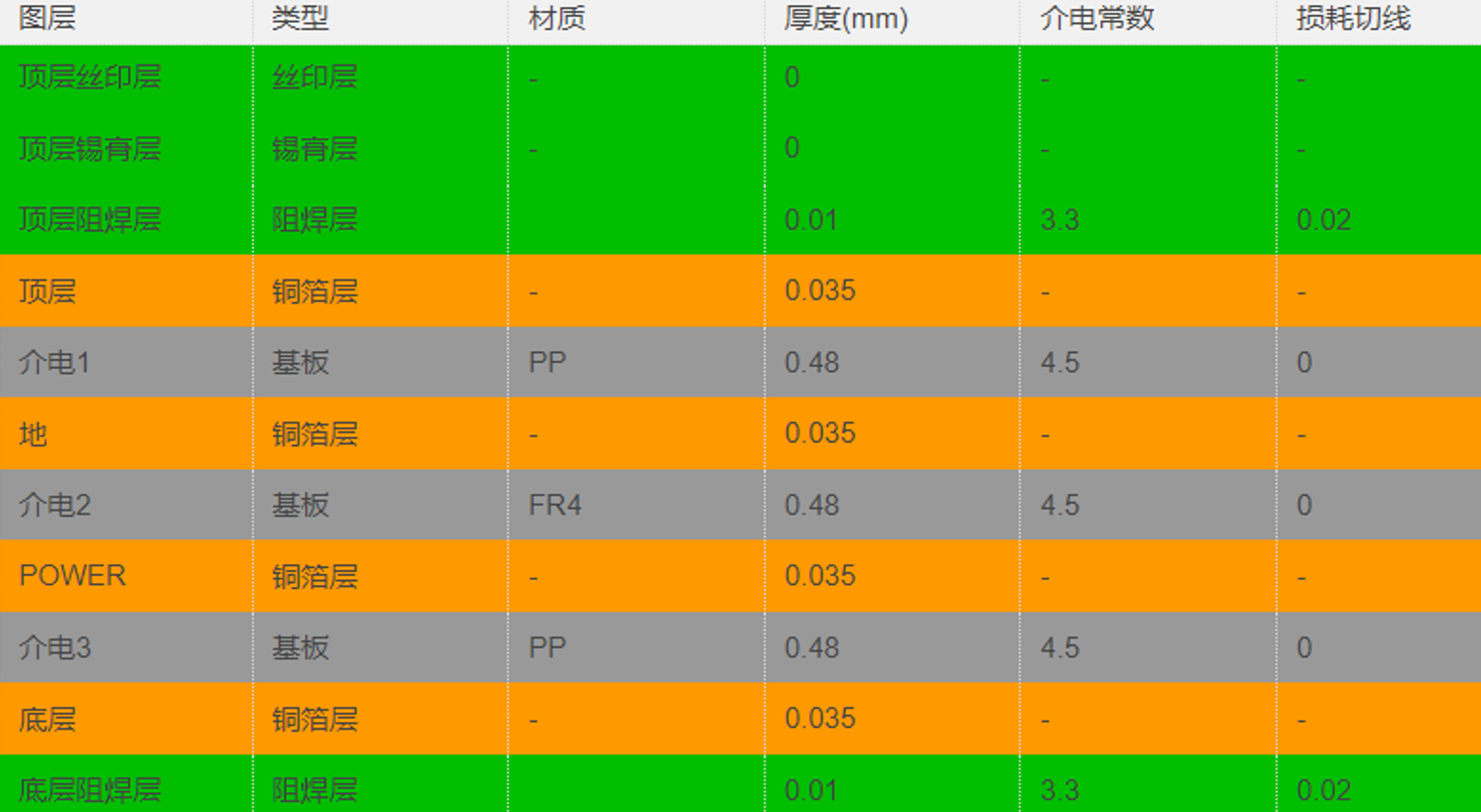

在实际工程设计当中,工艺参数一般由板厂提供,其包括介电常数、叠层间距、盖油厚度、叠层铜皮厚度等等参数。本设计使用嘉立创FR-4板材,7628叠层结构,具体的介电常数为4.6、顶层铜厚1oz、内层铜厚0.5oz、叠层间距0.2mm。将其输入Si9000进行计算,便可得到传输线阻抗信息与幅频特性,下图3-9与3-10分别予以描述。

根据给定的参数信息,软件最后计算的阻抗数值为49.66Ω,此时的顶层走线宽度为12.48mil,走线高度为1oz,满足设计需求。

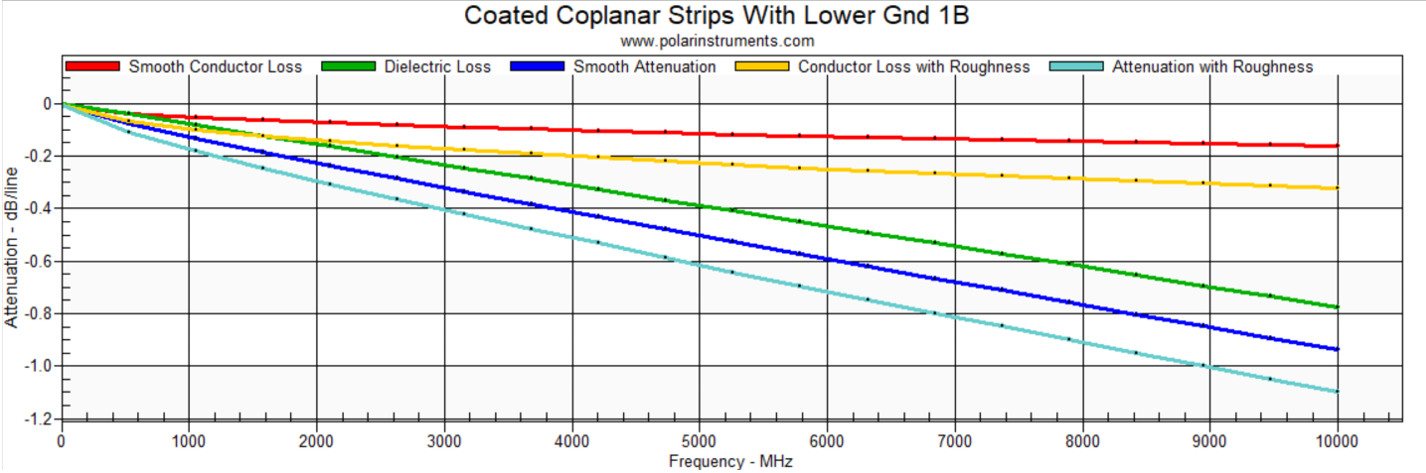

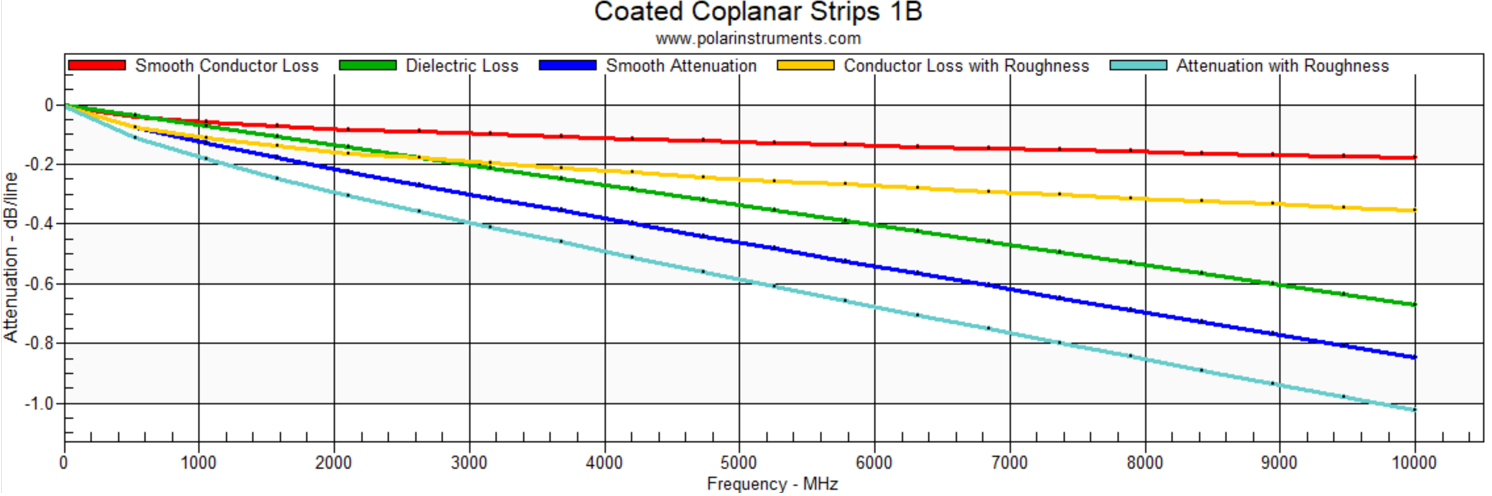

上图中,详细描述了走线工作频率与信号衰减的关系。可以发现随着工作频率的不断提高,信号衰减也在不断加大,在10GHz时将会在走线上衰减1.1dB。因此,在高频时需要将FR-4更换为插损更小的板材介质。注意对于微带线走线,伴随地可能会对阻抗造成较大的影响,参考海思硬件设计指南,伴地距离应当至少大于1.5倍线宽。

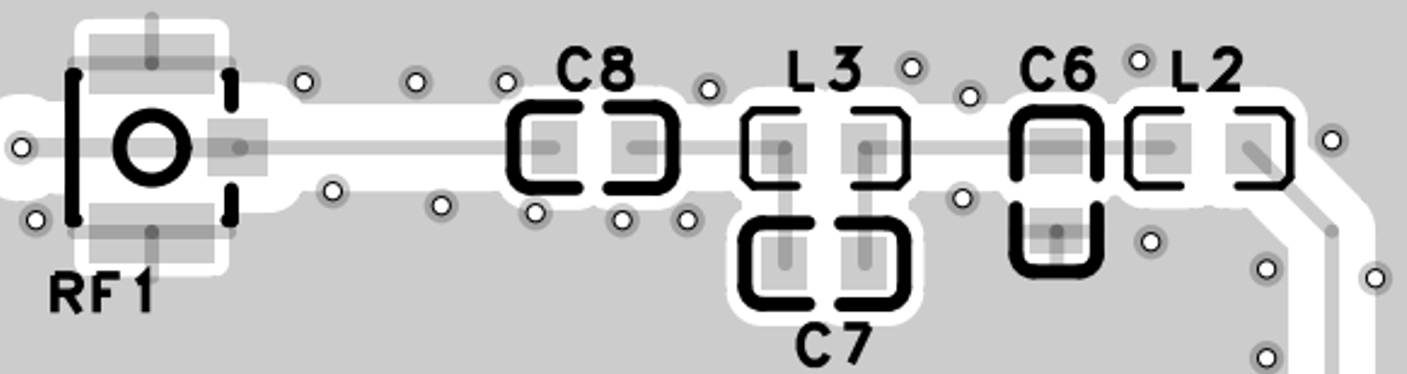

单层板阻抗匹配

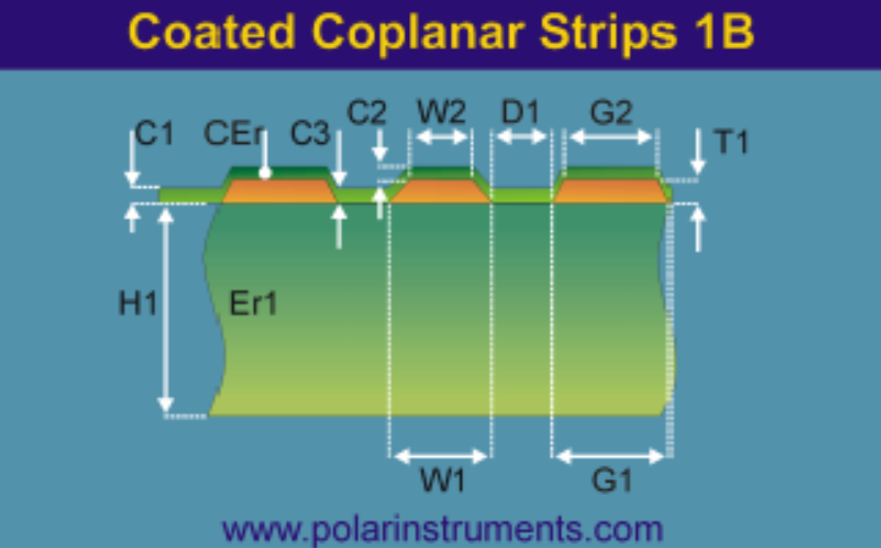

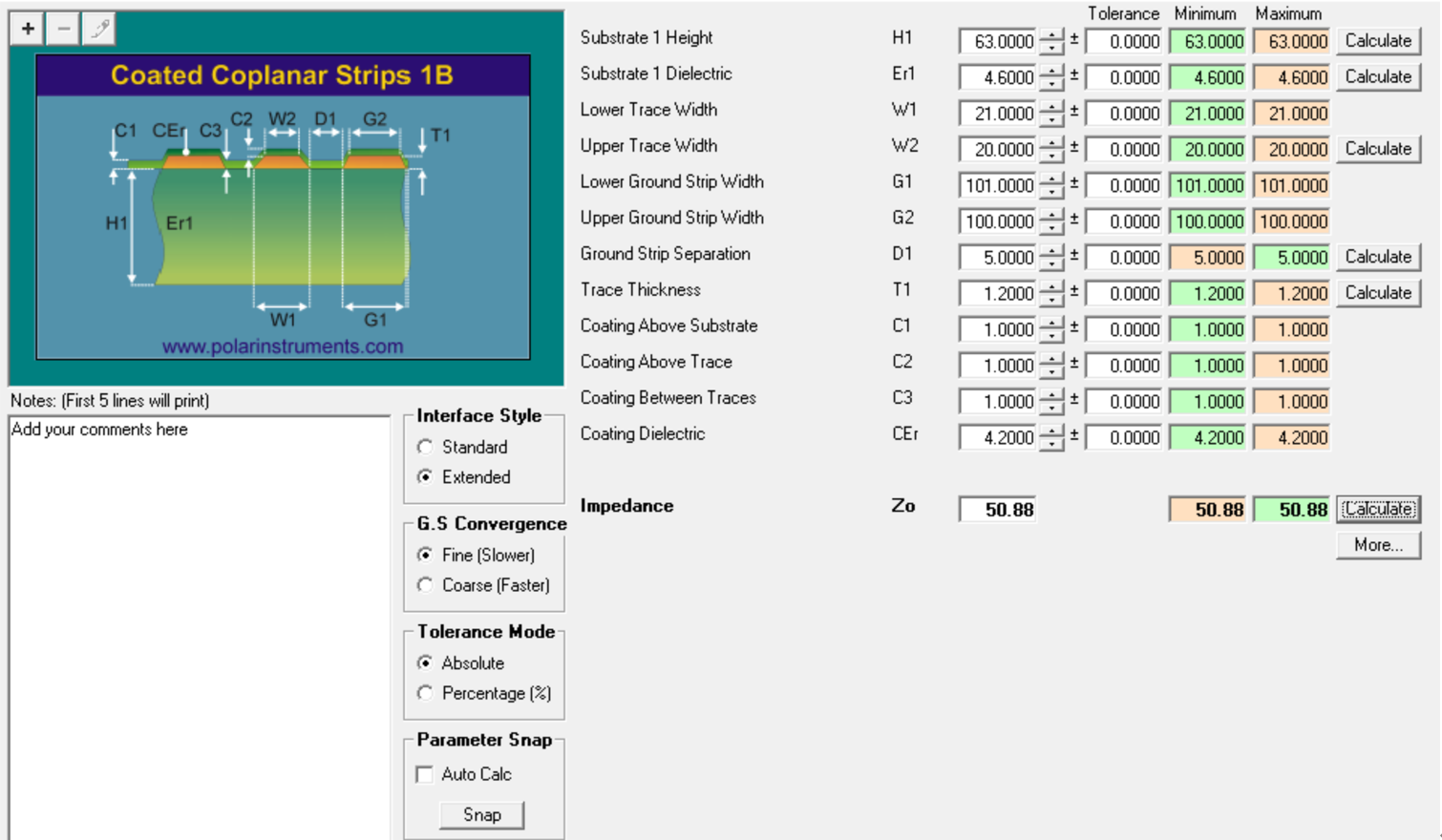

出于成本与制作工艺的考虑,使用双层板进行阻抗匹配电路设计的应用也较为广泛。不同于多层板的是,单/双层板的参考地平面距离走线很远,此时如果继续依据微带线的理论方法进行设计将会导致顶层走线的线宽变粗到不可接受的范围。因此,在单/双层板设计的过程中,往往会采用共面波导的设计方法,将走线旁的地平面也纳入计算当中去。一个典型的共面波导结构如图3-11所示,其中关键的参数主要包括:$H_1$厚度、$W_2$顶层走线宽度、$T_1$顶层走线高度、$D_1$走向到伴随地平面的距离。

将板厂提供的工艺参数导入设计软件计算,参考海思硬件设计手册设计伴随地距离为5mil,最后得出阻抗线宽度在0.503mm附近较为合适。

仿真不同频率下的线路损耗,可以发现其特性与微带线传输线相类似,均是随着频率提高衰减不断加大。

信号屏蔽

在数模混合电路中,数字电路的电流一般非常大且变化剧烈,而恰好模拟电路对噪声非常敏感。因此在电路设计中需要使用特殊手段来对数字与模拟电路进行隔离,避免数字电路对模拟电路部分的串扰。

接地

电路中所有电信号幅值的数值都是针对参考平面的零电势而言的,所以在电路设计中合理的接地是保证数字信号不被误判、模拟信号不被干扰的重要因素。前文针对数字电路与模拟电路部分信号特性都做了简要介绍,即数字电路变化速度快,典型的现代高速数字系统的上升时间可以轻松突破1ns;模拟电路的幅值小且对噪声敏感,一个典型的数字通信系统中输入信号的幅值往往可以低于-50dBm。如何将二者以合理的方式组合在一起,是现代高速数模混合电路中的重要挑战,而合理的接地又是实现高性能设计的关键部分。

注意,CMOS逻辑数字系统的快速上升时间往往还伴随着极高的数字信号带宽。对于方波信号的带宽计算我们往往计算五次谐波,典型情况下数字系统的电平上升时间为周期的7%。故信号带宽$BW$与上升时间$T_r$的乘积关系约为0.35,该经验公式被广泛应用于数字信号的带宽估计。从中我们可以推断出一个频率较低的信号往往并不意味着较低的带宽,这为整个数字系统的设计提供了重要依据。

参考地平面

在现代数模混合电路系统的设计中,往往会在多层PCB的叠层设计中单独指定一个完整的地平面,一方面可以用做微带线的阻抗参考平面,另外一方面可以为走线提供最近的回流路径。对于四层板,一般选用第二层作为参考地平面;对于六层板,一般会选用第二、五层作为参考地平面。本设计的发送子板与接收子板均采用四层设计,关键信号线均在顶层走线。PCB叠层结构从上到下依次为:信号顶层、地层、电源层、信号底层,叠层物理结构如图3-14所示。

过孔伴随地

在前一节中我们讨论了通过叠层结构设计出完整的参考地平面,在本节中我们将会讨论如何将信号的回流以最短路径引导到地平面。一个最简单高效的方法是大量的伴随过孔,通过将接地过孔不规则地分布在走线旁边,用以帮助信号回流到地。本设计中的接地过孔布局如图3-15所示,每条关键的射频线路旁均放置了大量的接地过孔,一方面可以提供最短的回流路径,另外一方面可以起到信号屏蔽的作用。但是注意,接地过孔与伴随地线与传输线的距离不要过近避免影响特征阻抗,也不能均匀放置避免形成共振腔体。

地隔离

前文提到数模混合电路中数字部分的强干扰性与模拟部分的敏感性,因此对于这两部分电路必须通过某种方式进行隔离。首先应当对二者的布局区域进行划分,保证不会因为物理距离过近造成串扰;其次应该保证二者的供电电源相互隔离,避免电源噪声对模拟部分的干扰;最后还应当为模拟地与数字地添加磁珠或0Ω电阻隔离。在本设计中STM32的模拟地与数字地之间通过磁珠连接,由于磁珠在高频下呈现阻性,因此可以有效抑制高频噪声的串扰。

退耦

随着半导体设计的工艺制程不断提高,现代数字芯片的片上晶体管间距不断缩小,因此晶体管之间的击穿电压也在不断降低。出于低功耗、高性能、制程工艺等方面的考虑,现代芯片的核心工作电压在不断降低,核心电流也在不断加大,如何在高负载、大电流的情况下保证供电的稳定成为了一个重要的问题。

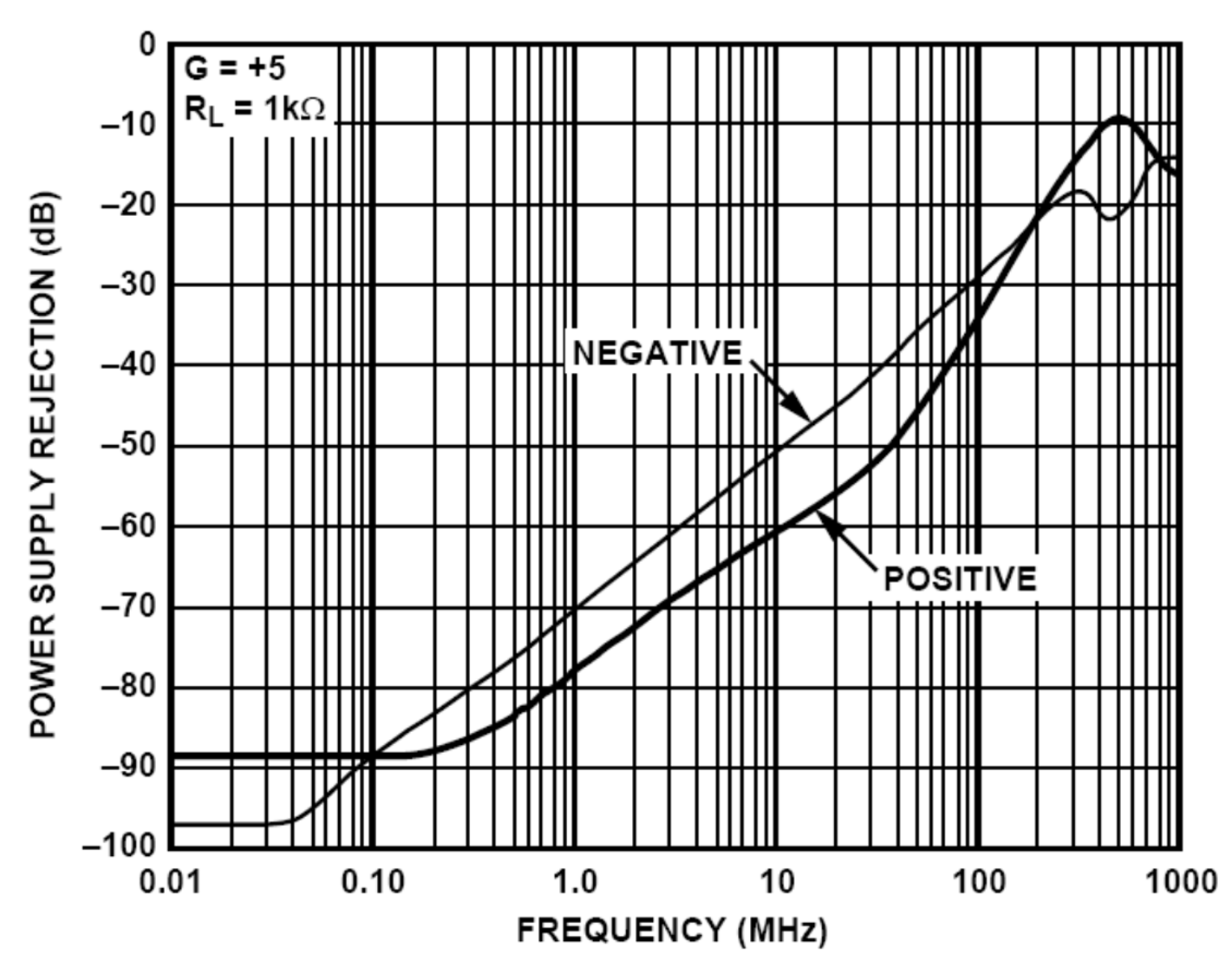

对于数字电路而言,电源的不稳定容易造成芯片工作的不正常,但只要波动在技术指标允许的范围内就一般不会造成逻辑错误;但是对于模拟芯片而言,所有的噪声与波动均会叠加在输出,照成输出端的干扰。一个衡量模拟芯片对电源噪声抑制能力的指标是PSRR,下图3-17也给出了一个高性能运放AD8099的PSRR抑制比与频率的关系。可以发现随着电源噪声频率的升高,该模拟芯片对噪声的抑制能力也在不断下降。

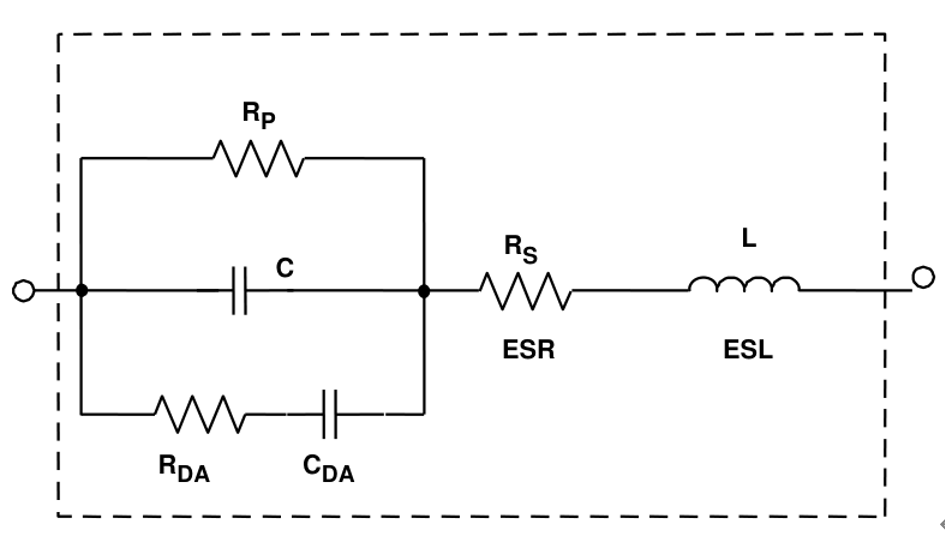

一个典型的电路设计中,电容一般拥有储能、滤波、隔直等功能,实现电源供应的稳定一般都依赖于芯片电源引脚附近的大量退耦电容来实现。一个典型的电容器等效电路如图3-18所示,其中$C$表示电容容值,$ESR$表示等效串联电阻,$ESL$表示等效串联电感,$R_p$表示绝缘电阻,$R_{DA}$与$C_{DA}$表示电介质吸收模型。

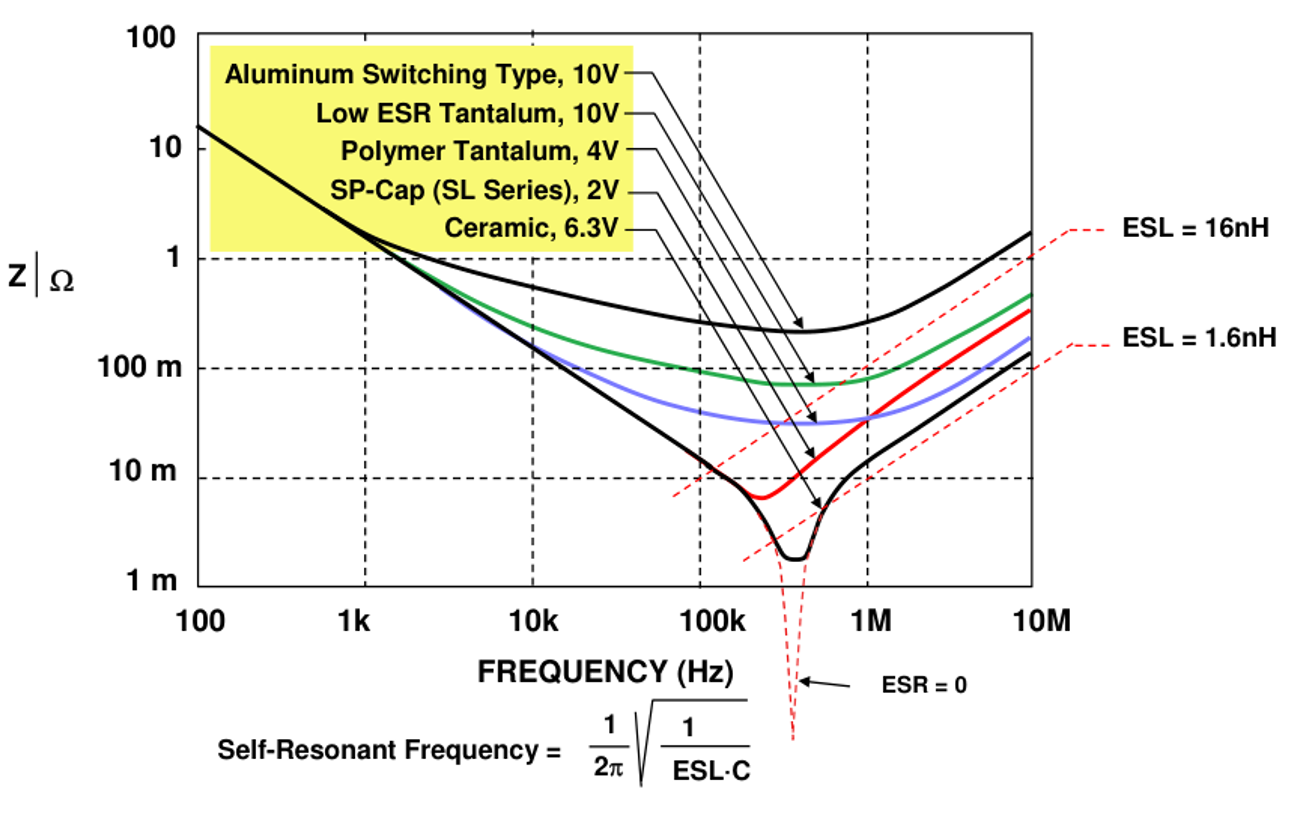

所以非理想电容在频率提高时阻抗会表现为先低后高的特性,在转折点之后由于串联电感的作用阻抗会不断加大。转折频率取决于$C$与$ESL$的数值,具体可以表示为:$ f_{resonance}=\frac{1}{2\pi}\sqrt{\frac{1}{ESL\ast C}} $,典型的阻抗频率关系如图3-19所示。

由于电容的非理想特性,在常见的电源退耦电路中常常通过一个容值较大的电容与容值较小的电容并联来实现,其中容值较小的电容负责高频下的退耦,容值较大的负责储能和低频退耦。

信号调理

由于模拟基带信号的输入输出分别通过3.5mm耳机孔与扬声器接口,因此需要对ADC与DAC的前端进行额外的调理,使其能够以适当的阻抗、功率、幅值范围连接外设。

输入调理

模拟基带信号输入调理的目的是为了将外部输入的信号调整到ADC的量程范围(0-3.3V)内,为了实现信号的调理我们需要同时使用运算放大器与模拟滤波器。模拟滤波器的设计在前文已经进行介绍,下文将详细介绍运算放大器的设计与仿真。

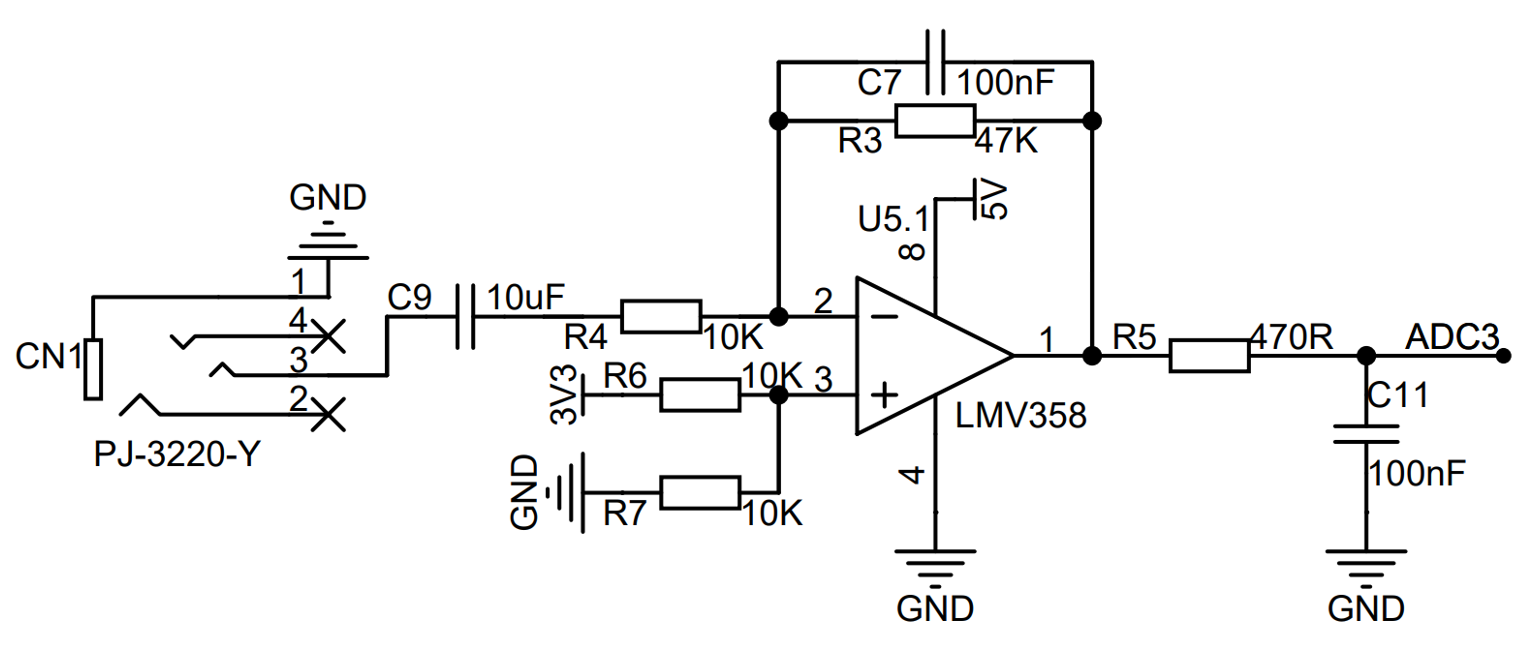

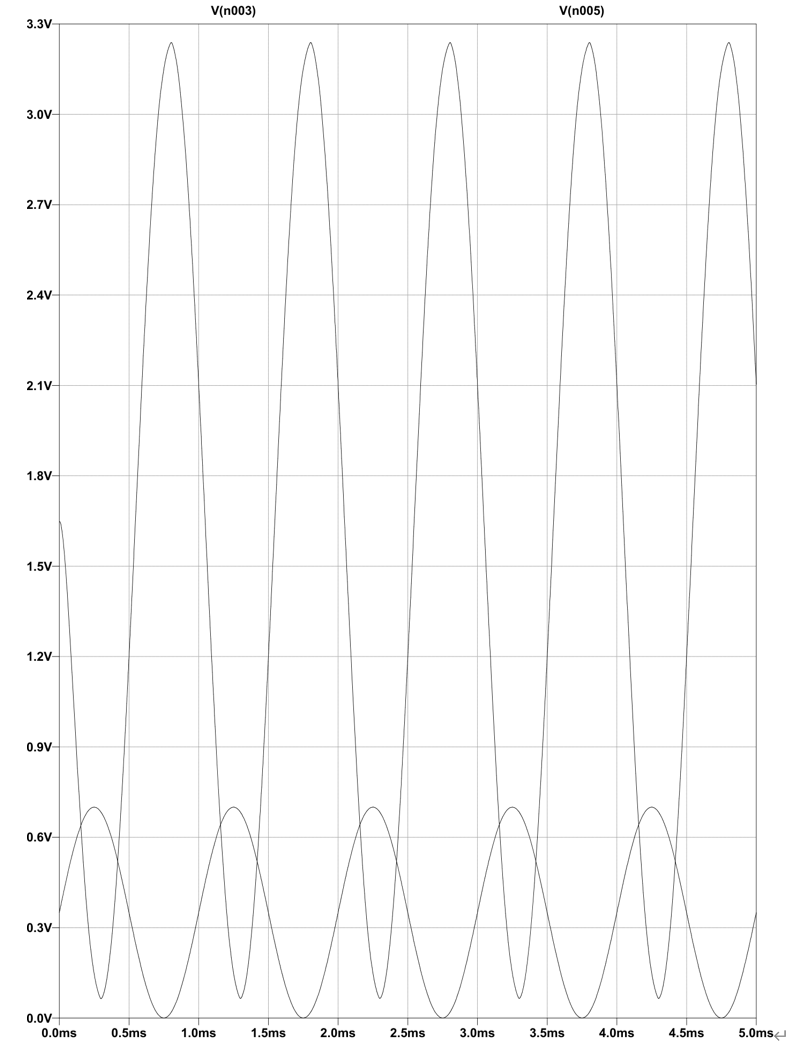

一个典型的3.5mm音频系统,其在接近满音量时输出的电压幅值为1V左右。要想将这样的音频系统转换为0-3.3V的系统则至少需要一个放大倍率为3倍的放大器,在实际应用中这个数值可以略大以保证可以降低输入端音量,提高输入端功放的线性度。由于本系统主要为3.3V供电,因此在放大器方面选择经典LM358的低电压版LMV358,其可提供完整的单电源供电与轨到轨特性。本设计中输入信号的调理部分原理图如图3-20所示。

运算放大器在模拟电路中的应用非常广泛,包括放大、滤波、运算、跟随等功能。一个理想的运算放大器的放大倍率无限大、输入阻抗无限大、输出阻抗无限小,实际的运放也确实能在一定的范围内趋近于理想。这就使得其具备理想源和负载的特性,对其的分析也依靠虚短、虚断的特性由复杂的非线性分析转换为简单的线性分析。因此对于上图的反向放大器,其输入输出信号的幅值满足$V_o=-V_i*\frac{R_3}{R_4}$。

因此上述电路的主要功能是一个4.7倍的反向放大,其中C7主要用于对信号传播过程中的相位补偿,增加电路的稳定性;C9主要用于输入信号的直流隔离。因为运放同向和反向输入端拥有虚短的特性,所以R6、R7的分压将会加载反相输入端上,为运放输出也提供一个1.65V的偏置信号。输出级的R5与C11在前文已做论述,二者共同构成了ADC输入级的抗混叠滤波器,用以避免带外信号的干扰。对上述电路进行瞬态仿真,输入激励为峰值1Vpp、偏置0.5Vpp、频率1KHz的正弦波信号,观察输出端信号的波形。下图3-21中原始输入0.7Vpp的信号被放大到接近3.3Vpp,完成了模拟信号的输入调理。

输出调理

输出调理部分主要用于信号从DAC到扬声器路径上的信号调理,整个调理的目的是为了使解调后的模拟信号拥有更小的输出阻抗、更少的带外杂散与更大的输出功率。对于STM32的片上DAC而言,其在开启输出缓冲器后的输出阻抗约为15KΩ,这样的阻抗对于一个典型负载而言过大。因此在输出到滤波器前需要进行一级电压跟随,用以将较大的输出阻抗转换为较小的输出阻抗,即将非理想源转换为理想源。

电压跟随器与滤波器的电路如图3-22所示,可以看见运放的反向输入端与输出端直接连接在一起,这就使得输出端的信号与同向输入端相同,起到电压跟随的作用。对于后级模拟滤波器不再赘述,此处是为了滤除带外噪声干扰。

功放部分的芯片则采用常见的FM8002A,其是一枚单通道2W功率的放大器。该芯片内置两个运放,通过外围反馈电阻来设置增益。其内部结构如图3-23所示。

由于内置两颗运算放大器,所以其通过外部反馈电阻配置的输出增益$A_{ud}$可以表示为:$A_{ud}=2*\frac{R_f}{R_i}$。在本设计中通过配置电阻阻值均为20KΩ实现了2倍的信号放大,电路图如图3-24所示,其中H4用于外接扬声器使用。

其它

前文所述的滤波器设计、阻抗匹配、信号屏蔽和信号调理都是针对射频与高速信号而需要特别考虑的问题,对于低频信号这些问题大可不做考虑。本设计的低频部分主要集中在核心板与射频芯片的控制线上,对于这部分走线一般无特殊要求。但在设计时仍需考虑完整的输入保护与电源退耦、较短的时钟走线、友好的布局策略等原则。

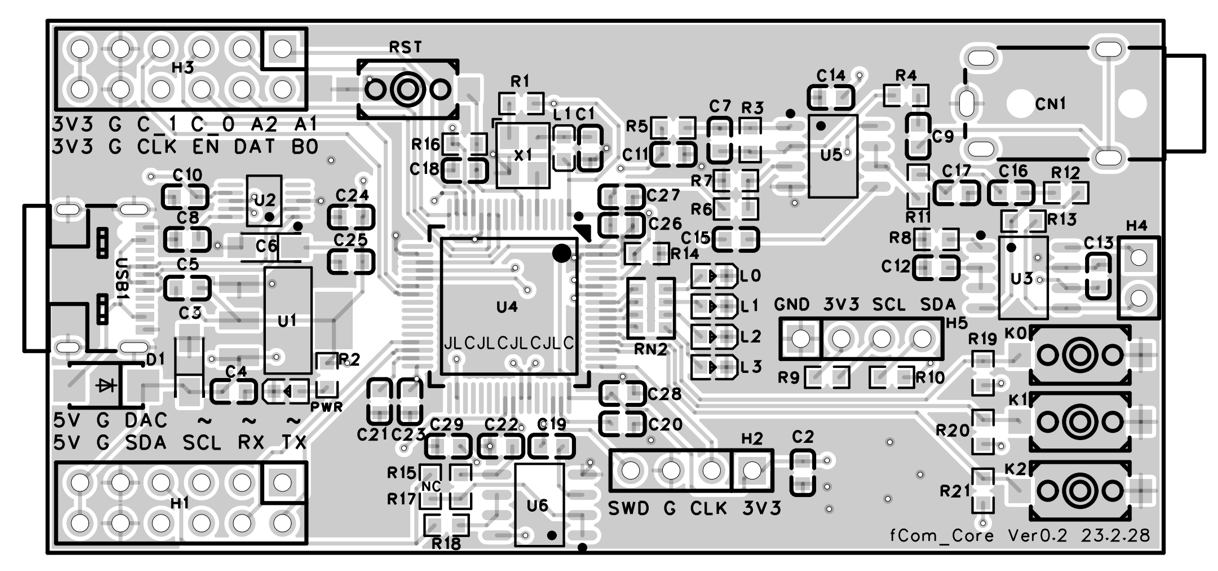

下图3-25便是本设计中核心板的布局布线影印图,布局以主控芯片为核心向四周延伸,模块的连接端口位于左侧供发射与接收子板连接,右侧则主要布局人机交互接口用于模拟信号采集与产生,以及系统参数的调节。

在布局退耦电容时,电容应当尽可能地靠近芯片供电引脚以使得芯片在高负载工作时可以较快从电源中获得电流。如果条件允许,可以考虑同时放置大小两颗电容,其中容值较大的电容用于高频退耦,容值较小的则用于低频下的储能。

此处的时钟由有源晶振提供以获得最稳定的时钟输入,在有源晶振的电源输入端布局了完整的退耦电路与磁珠隔离,用以保证输入晶振的电源稳定,晶振输出的时钟可靠。此外,晶振的布局也尽可能地靠近MCU,用以保证时钟进入MCU的路径无干扰。

4、软件开发

本设计的软件开发主要分为三个部分,即外设驱动、解调与调制。其中外设驱动部分主要涉及STM32对片上以及片外外设的控制与数据交互,例如通过SPI控制MSi001的频点、通过片上ADC采集数据、通过IIC控制发送模块的载波等功能;解调模块用来对下变频后的基带信号进行解调与滤波操作,最终能得到调制前的原始模拟信号;调制模块用来对采集到的模拟基带信号进行调制,配合发射子板实现信号的上变频与发射。软件部分的模块结构图如图4-1所示,所有的软件均在STM32F405上实现。

外设驱动

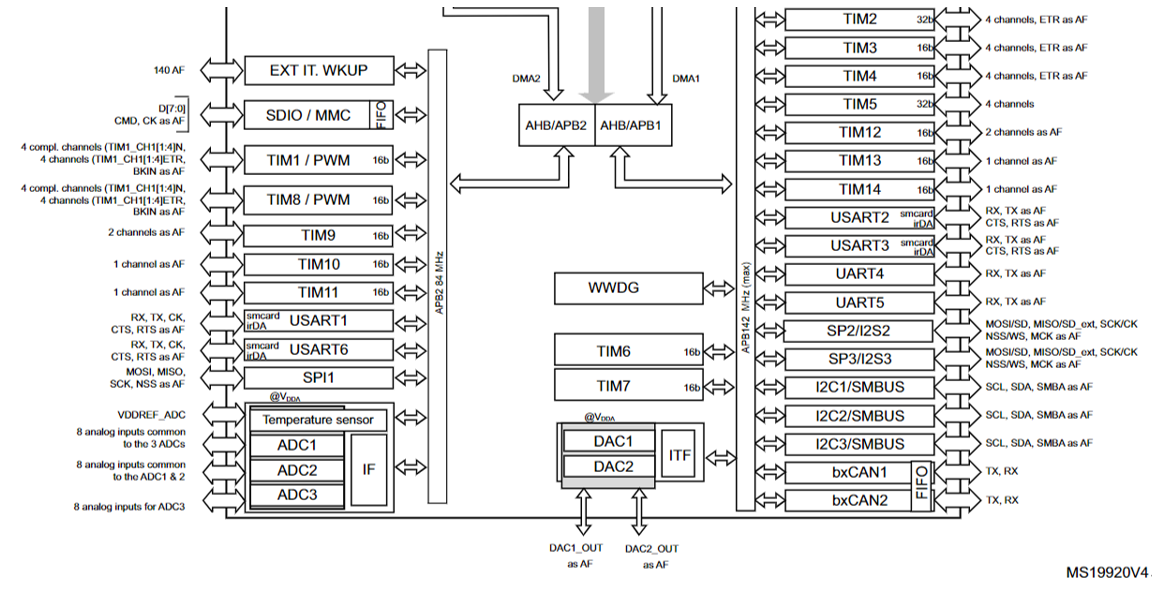

芯片与外围器件的交互往往通过可以通过GPIO口模拟实现,但为了追求更高的效率与更简单的操作往往会借助片上外设来实现。STM32F4作为意法半导体公司的高性能MCU,其片上外设的数量、种类与性能都在MCU中有较高的可用性。本设计使用的STM32F405RGT6的芯片内部的总线框架如图4-2所示。

本节的主要内容是介绍设计中片上与片外外设的架构与使用方法,具体需要使用到的片上外设为SPI、IIC、TIM、ADC、DAC、NVIC、UART与DMA,需要使用到的片外外设为MSi001、Si5351、CH340E与0.96寸OLED屏。

片上外设

STM32以及其他MCU的片上外设一般都是硬件外设,即固化在ASIC内部的逻辑电路。其一般拥有较好的性能与较简单的使用方法,通过配置外设寄存器便可实现外设的初始化与通信。因为本设计涉及大量的信号处理内容,因此必须借助硬件外设来实现高效的数据搬移与处理。下面将举例介绍ADC采集所用到的软件架构,其它外设的使用较为简单不再赘述。

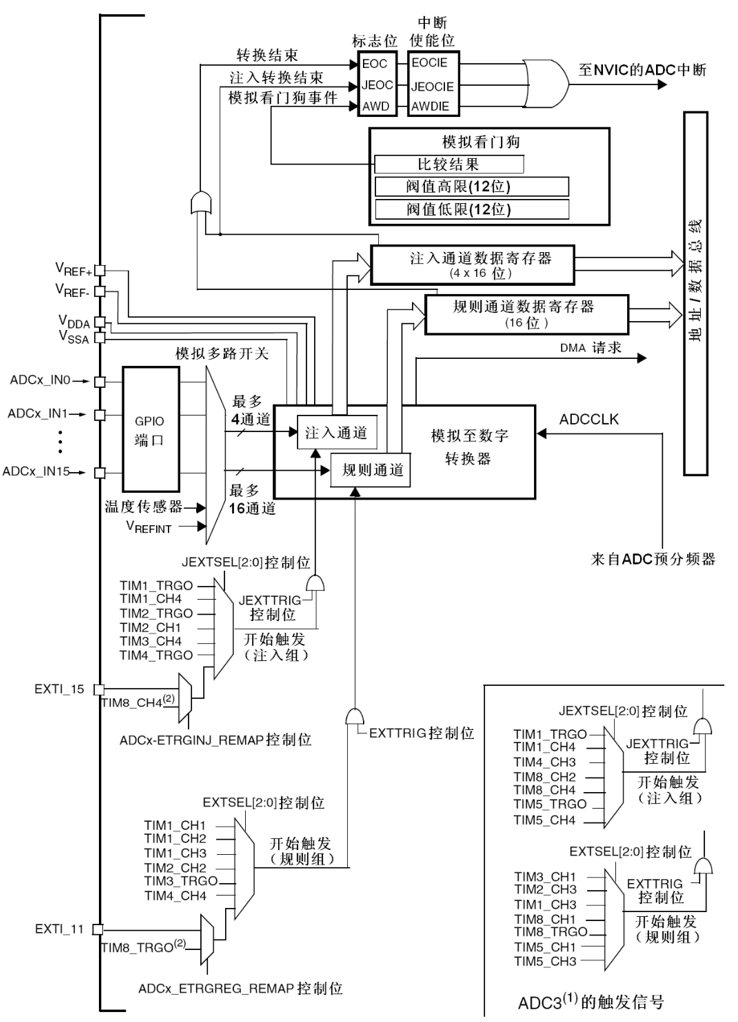

由于MSi001的零中频模式最低可配置的中频滤波器带宽为200KHz,因此要想不失真地采集到基带信号就必须保证采样率大于等与二倍的信号带宽。在本设计中对I与Q路通道的采集均使用500KHz,即双路500KHz、12Bit采样率ADC。这样的数据吞吐量对于单片机而言是极为庞大的,无法再通过中断的方法手动搬移数据,必须借助硬件实现。观察STM32F4的ADC外设可以发现其内置了DMA模块,该模块可以在CPU不介入的时候完成外设到内存与内存到内存的数据搬移。下图展示了该芯片内部的ADC模块:

我们希望数据采样的整个流程不需要CPU参与,完全通过硬件实现自动化。因此根据前文的ADC结构框图,我们可以得出下面一个合理的数据流架构:通过TIM3定时器触发ADC1/2采样,数据通过DMA2自动搬移到系统内存供后续解调。

在实际的工程项目中可以通过库函数来实现外设的寄存器配置,也可以通过工具辅助配置。在此我们使用STM32CubeMX来辅助外设的配置,通过鼠标点选的方式快速地配置参数。

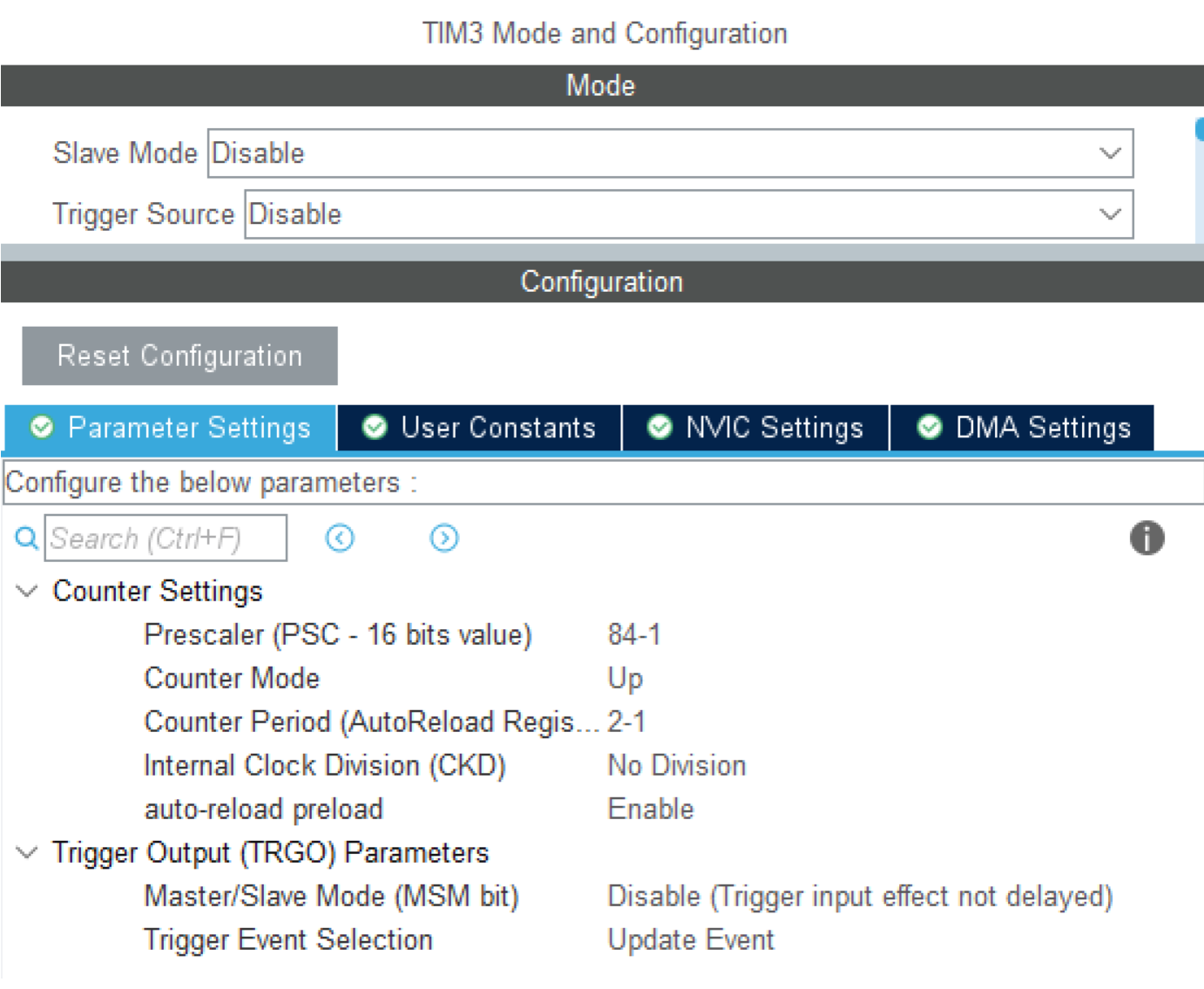

TIM3配置:定时器用于触发ADC采样,触发频率取决于定时器工作时钟$f_clk$,分频系数$psc$,自动重转载值$arr$。由上述参数可以推得定时器的事件更新频率$f_{update}$可以表述为:$f_{update}=\frac{f_{clk}}{(psc+1)*(arr+1)}$。在本设计中$f_update$为ADC采样率500KHz,$f_clk$为TIM3外设频率84MHz,故当$psc=83,arr=1$时可以获得500KHz的定时更新频率,具体的配置信息展示如图4-4。

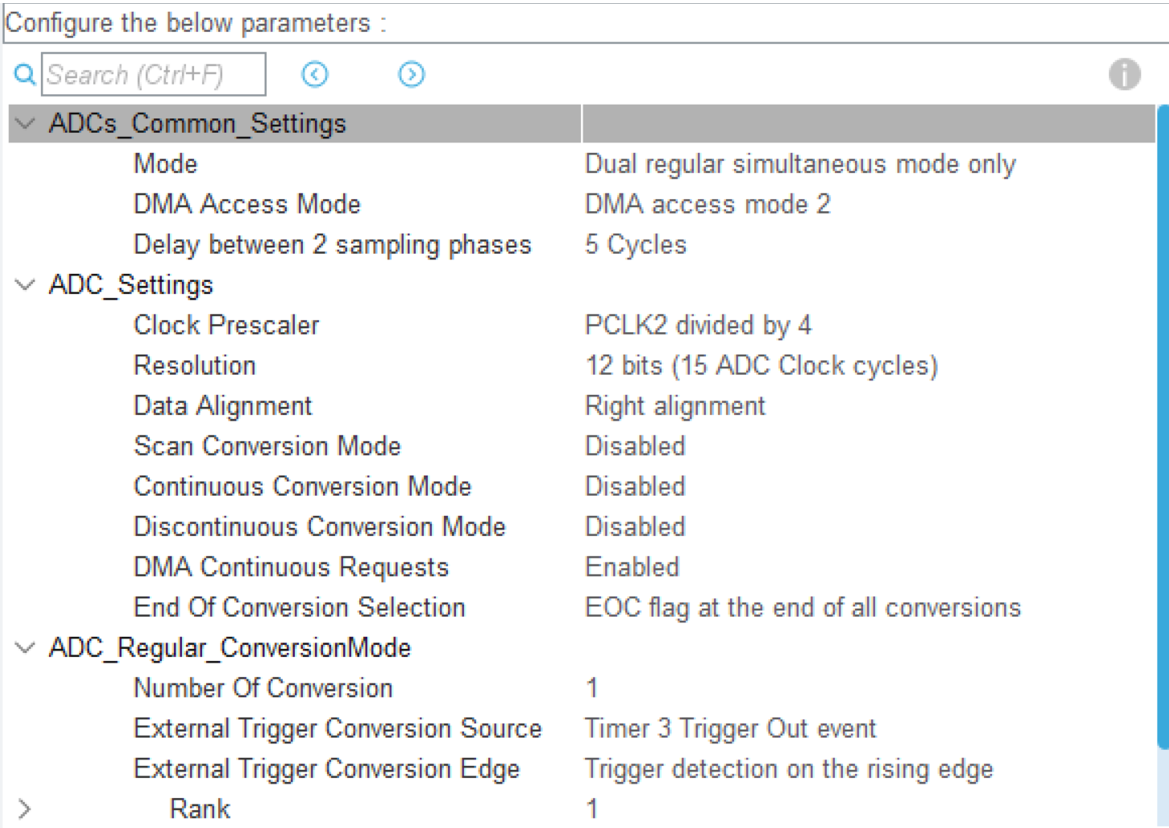

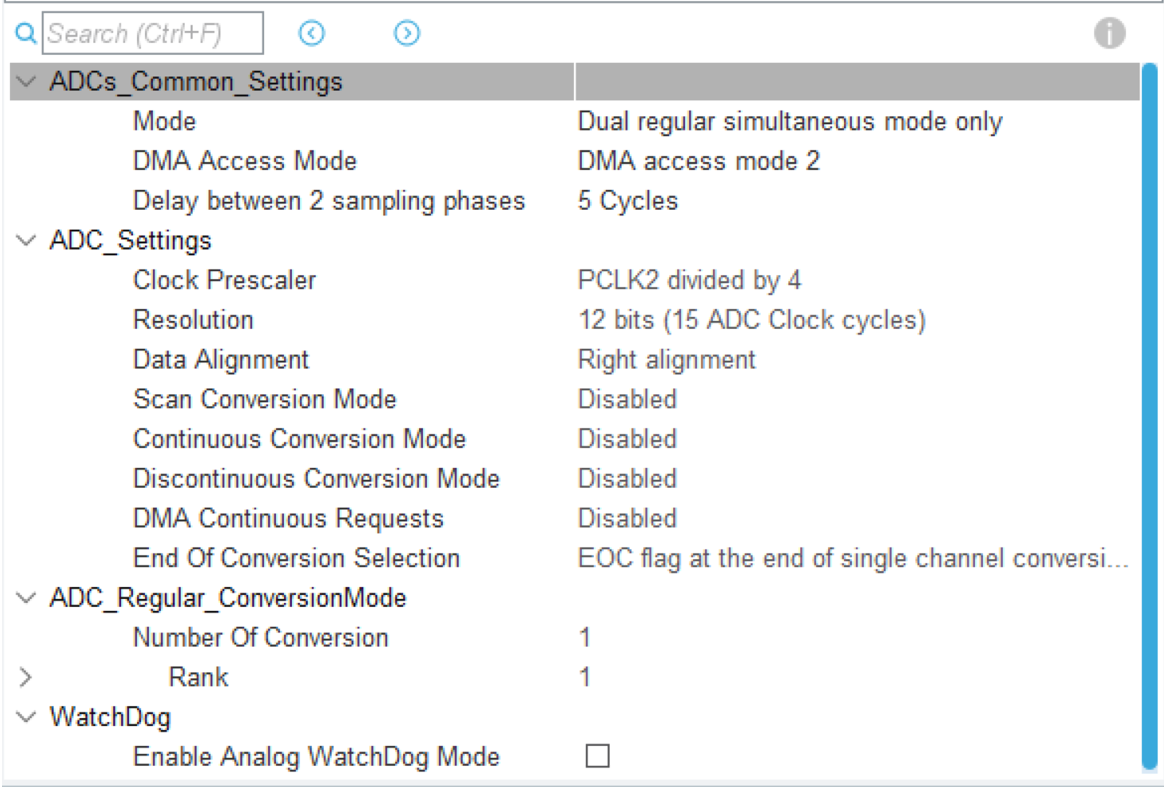

ADC1/2配置:ADC外设用于模拟信号的采样,在本设计中共使用到3个ADC模块,分别用于基带IQ信号的采集与输入模拟信号的采集,本节中我们只介绍IQ信号采集所用到的两个ADC。因为我们追求最高效率的ADC采样架构,因此可以在ADC初始化配置时启用“Dual regular simultaneous”模式来进同步采样。采样的触发源来自TIM3的事件触发输出,DMA工作在环回模式。ADC1、2两个外设的具体配置信息展示如图4-5与图4-6,注意在同步采样时ADC2可以看作是ADC1的从ADC,因此ADC2无需配置触发源。

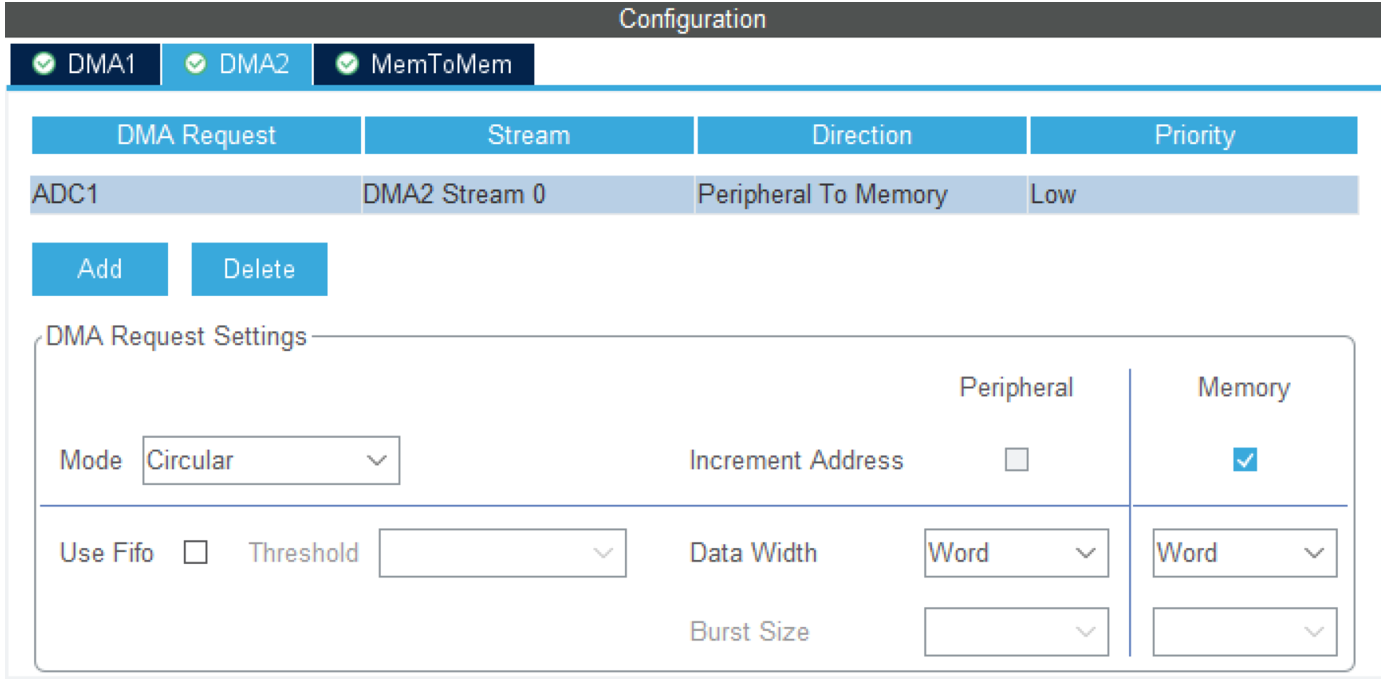

DMA配置:DMA可以在实现CPU不干预情况下的高效率数据搬移,搬移方向可以是内存到外设也可以是内存到内存。在本设计中,单次ADC采样的数据是ADC1与ADC2的拼接,所以数据宽度选用Word;因为ADC的采样持续进行,因此指定DMA工作模式为环回模式。

配置完成后导出到Keil工程,再通过简单的几条代码对外设进行开启与配置。核心代码如下所示,分别进行从ADC开启、ADC DMA转换模式配置与定时器启动三个步骤。

HAL_ADC_Start(&hadc2);

HAL_ADCEx_MultiModeStart_DMA(&hadc1,adc_cap_dat,ADC_CAP_LENGTH);

HAL_TIM_Base_Start(&htim3);片外外设

MCU对片外外设的配置主要通过SPI、IIC这类通信接口实现,在本项目中SPI接口使用硬件外设实现,IIC接口出于灵活性使用软件模拟。本节主要介绍MSi001的配置,对于OLED与Si5351的配置较为简单不再赘述。

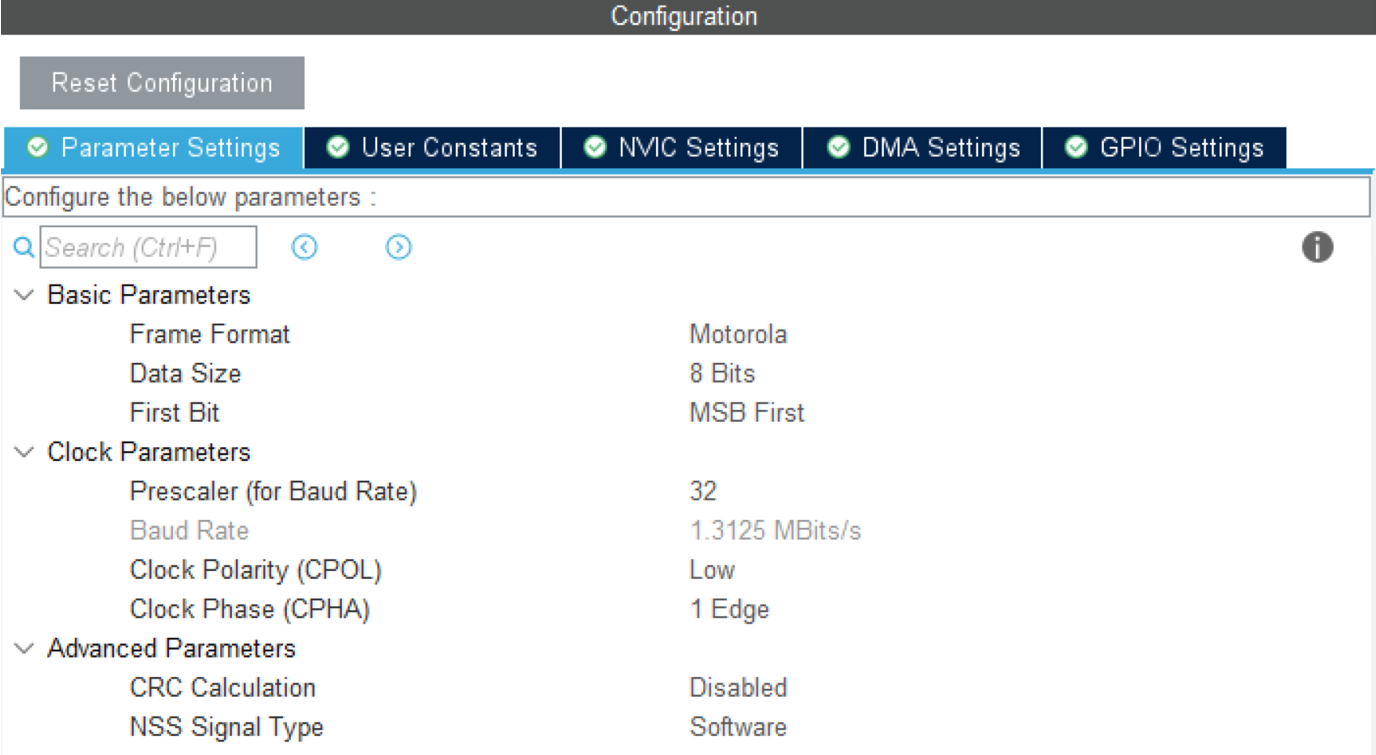

MSi001是一块工作频率在0-2GHz范围内的集成调谐器,在本设计中我们主要借助其可配置频率的特性实现信号接收部分的前端调理。具体的配置流程图如下所示,共需要配置7个寄存器。该芯片的配置通过SPI协议实现,单帧数据长度为24位。数据格式为MSB First,每帧数据将会在EN的上升沿进行锁存与生效。对于SPI硬件外设的配置可以参考图4-8,工作模式为MSB First,CPOL为Low,CPHA为1 Edge。

在典型的FM接收系统中由于信息只与频率有关,所以LNA数值可以固定为最大,衰减器数值为最小,工作模式为零中频,中频滤波器带宽为200KHz。故在此处我们只以99MHz为例介绍频率相关的寄存器配置,即BAND、INT与FRAC三者。

频段BAND

由于MSi001对各个频段都进行了性能优化,所以在进行信号接收时可以依据信号频率选择最佳频段。由于不同频段对应的LO分频系统也存在差异,所以将会导致后文对INT以及FRAC的计算存在差异。信号输入频段的选择有寄存器0的11-4位来配置,具体模式配置信息如下表4-1所示。由于工作频率为99MHz,频率范围在VHF_MODE下,故配置寄存0的11-4位为0100 0010,此时本振分频系数为32。

| Reg 0[11:4] | Mode Name | LO Division |

|---|---|---|

| 0110 0001 | AM_MODE1 | 16 |

| 1110 0001 | AM_MODE2 | 16 |

| 0100 0010 | VHF_MODE | 32 |

| 0100 0100 | B3_MODE | 16 |

| 0100 1000 | B45_MODE | 4 |

| 0101 0000 | BL_MODE | 2 |

整数分频INT

MSi001的工作频率由锁相环产生,因此对频率的配置本质上就是对分频系数的配置。在确定分频系数之前,需要先确定系统的工作频率,工作频率则由载波频率$f_{rf}$与中频频率$f_{if}$共同确定。对于AM频段,本振频率可以表示为:$f_{lo}=f_{rf}+f_{if}+f_{if1}$,其他频段下本振频率可以表示为:$f_{lo}=f_{rf}+f_{if}$。

在确定输入载波频率与中频频率之后,PLL工作频率$f_{synth}$可以表示为:$f_{synth}=\frac{f_{lo}}{lo_{div}}$。对于99MHz、200KHz、VHF频段的信号而言,PLL工作频率为3174.4MHz。

配置分频系数的第一步是配置整数分频系数INT,该数值由外部参考信号频率与PLL工作频率共同决定,可以表示为:$INT=[\frac{f_{synth}}{4*f_{ref}}]$。本设计中外部参考为24MHz,故可以得到整数分频系数INT的数值为33。

为了实现更精确的频率综合,第二需要进行小数分频系数FRAC的配置。一般情况下默认配置THRESH与FRAC数值最大以获得最小的频率步进,此时FRAC的数值可以表示为:$FRAC=\frac{\frac{f_{synth}}{4*f_{ref}}-INT}{4095}$。在本设计中,FRAC的数值为1228。

至此,完成了MSi001对频率的配置。本设计中,当设定频率为99.9MHz时候,串口会打印调试信息为:“FREQ = 99.9MHz, STEP = 0.7326KHz, AFC = 0.1789Hz, INT = 33, FRAC = 1228”,表明完成了正常的配置流程。

信号解调

基带IQ信号经过ADC采样进入单片机,采样率均为500KHz。前文我们已经通过STM32的片上外设实现了信号的高效采集与搬移,在本节中我们将探讨高效的信号解调架构。

本设计所采用的解调方式为非相干解调,通过近似计算将反正切计算转换为简单的乘法与加减法计算。为了进一步提高解调效率,本设计还对ADC采样与解调进行了缓冲区划分,借助类乒乓操作实现了分时计算。在解调完成后,数据还经过了一次简单的下采样与FIR滤波,最后在通过DAC输出。

解调原理

模拟调制通过模拟基带信号直接控制载波的某些参数,使得信息通过载波在高频处传输。通过控制的参数不同,可分为幅度调制(AM),频率调制(FM)与相位调制(PM)。其中PM与FM之间关系密切,区别只是PM信号的相位与调制信号正比而FM信号的相位与其积分成正比。一个典型的FM信号可表述如下式。

上式是一个典型的FM信号包括实部与虚部,当通过调谐器后信号分为两路,即I/Q两路正交信号。正交信号的表达式如下式所示,其中I表示同相信号,Q则表示正交信号。

在基带对上述正交信号进行微分,得到信号表述如下式表示:

通过对I/Q路信号相乘可得到信号如下式表示:

若需得到原始的基带信号,需要在上式表述的信号中去除余弦项,相减后信号的表达式如下式所示。

因为FM调制信号的幅度保持不变,仅依靠频率的变化表示信息。故上式中的信号与原始的基带信号仅相差一个恒定的常数项,在实际应用中仅仅表现为增益的变化,通过AGC后这种增益变化的影响消失。上述讨论的是在连续系统中对信号进行微分,体现到离散的数字系统中微分可以表述为信号之间的差分,即为下式所表述。

$$ \frac{d x(t)}{d t} \approx \frac{x[n]-x[n-2]}{2 T_{S}} $$

当上述表达式中的$T_s$趋近于0时,信号在此处的微分等于二者的数字域差分。故上述的FM解调原理可表述为下式。

同样地,由于FM信号的幅度近似保持不变,故解调后的信号相当于加上了一个固定增益。FM的解调也就近似化为一种只包含差分、减法、乘法的运算,在一次完整的运算中仅消耗两个乘法器,非常便于解调算法的工程实现。

解调实现

FM解调的理论依据在前文已经给出,本节将会介绍该算法的C语言工程实现。下文列出了解调过程中的关键代码,整个解调过程只使用到I路与Q路的当前与过去一个时刻的采样值。

//将IQ路数据进行解调并输出

void fm_signal_demod(float *i_dat, float *q_dat, float *out, uint16_t len){

for(uint16_t i = 1; i < len; i++){

out[i] = i_dat[i-1]*q_dat[i] - i_dat[i]*q_dat[i-1];

}

out[0] = out[1]; //第一位的数值直接进行幅值

}为了进一步提高解调架构的效率,在此处将参考ASIC设计中的乒乓操作对采样与解调数据空间进行划分。本设计通过ADC采样的过半回调函数实现空间划分,即当ADC缓冲区使用一半时就进入回调函数开始解调前一半空间的数据,此时后一半空间仍被用来缓冲采样。同样地当采样完成后仍会进入回调函数,此时解调后一半空间的采样值,前一半空间被用来缓冲采样。两个核心的回调函数举例如下,在实际设计时回调函数中仅保留标识符避免过量占用中断资源。

void HAL_ADC_ConvHalfCpltCallback(ADC_HandleTypeDef *hadc){

flag_cap = 1;

}

void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef *hadc){

flag_cap = 2;

}下采样与FIR

FM解调完成后得到原始基带信号,此时原始基带信号的采样率仍为500KHz,而基带信号频率只分布在0-3.4KHz附近。可以看出此时数字信号的采样率严重过剩,因此在解调完成后应当立即进行下采样操作以减小MCU负担。在经典的DSP处理中数据的下采样往往通过CIC滤波器进行,在此处为了减少运算压力直接间隔点提取数值实现下采样。本设计的下采样倍率为25倍,下采样后的采样率为20KHz,核心代码展示如下。

//对IQ路数据进行下变频,下变频比例为DOWNSAMPLE_RATE

for(uint16_t i = (ADC_CAP_LENGTH/2)/DOWNSAMPLE_RATE;i < ADC_CAP_LENGTH/DOWNSAMPLE_RATE;i++){

//对下变频缓冲区进行幅值

fm_down_dat[fm_down_index]=0;

for(uint16_t j = 0;j < DOWNSAMPLE_RATE;j++){

fm_down_dat[fm_down_index] += fm_demod_dat[i*DOWNSAMPLE_RATE+j];

}

fm_down_dat[fm_down_index] = fm_down_dat[fm_down_index]/DOWNSAMPLE_RATE;

//设置下变频缓冲区标识符

fm_down_index++;

if(fm_down_index == DOWNSAMPLE_LENGTH/2){

flag_process = 1;

}else if(fm_down_index == DOWNSAMPLE_LENGTH){

flag_process = 2;

fm_down_index = 0;

}

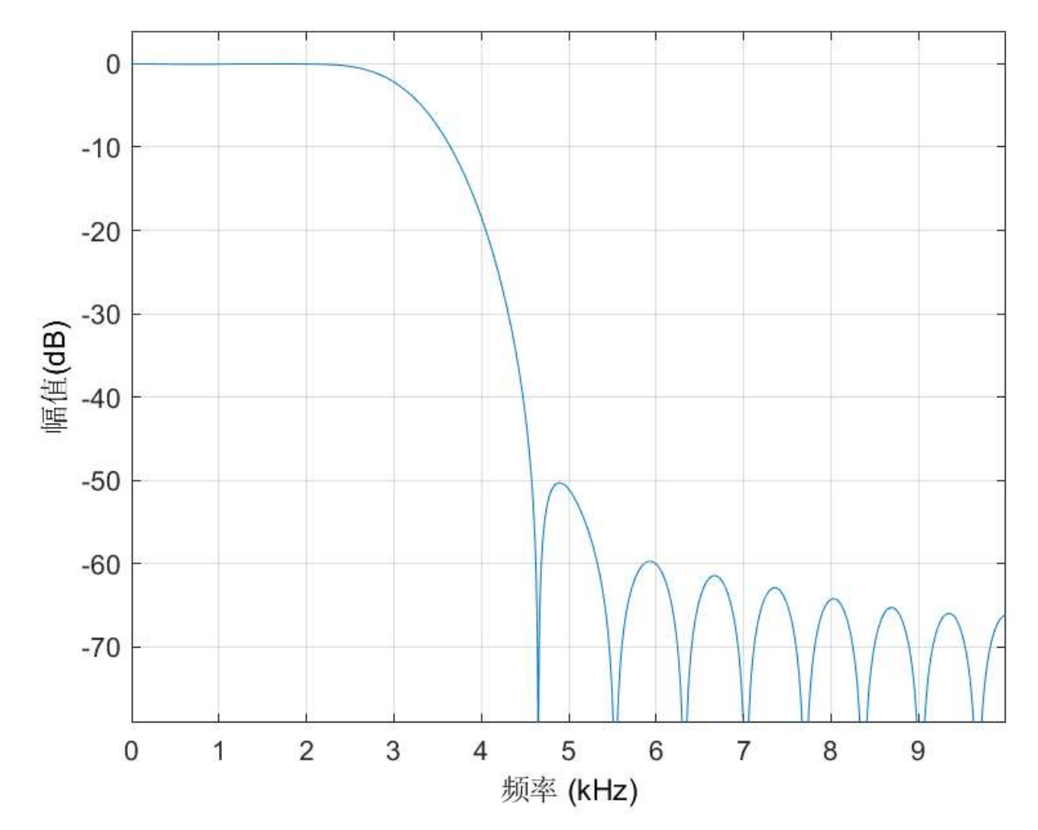

}下采样完成后的信号已经拥有了较好的信噪比,但仍存在一定的噪声,在本设计中将会通过FIR滤波器进一步滤除带外的干扰信号。滤波器的系数由MATLAB导出,直接使用CMSIS的DSP库在浮点下进行计算。滤波器的设计参数为:FIR低通、窗函数设计、20KHz采样率、截止频率3.4KHz、阶数30。MATLAB设计的滤波器幅频响应曲线如图4-9所示,可以看到在3.4KHz附近由明显衰减,阻带纹波衰减大于50dB,符合设计要求。

系数导出完成后,可以直接使用CMSIS DSP库中的FIR滤波函数进行滤波处理,关键代码列举如下。

//20K sample 3.4K cutoff

const float32_t COE_F32[29] = {

0.001241662656, 0.002164762933,0.0008259368478,-0.003793924814,-0.007643622346,

-0.002249721903, 0.01337968279, 0.02276735567, 0.004259234294, -0.03798524663,

-0.05936728045,-0.005976970308, 0.1279000342, 0.2749517858, 0.3390526175,

0.2749517858, 0.1279000342,-0.005976970308, -0.05936728045, -0.03798524663,

0.004259234294, 0.02276735567, 0.01337968279,-0.002249721903,-0.007643622346,

-0.003793924814,0.0008259368478, 0.002164762933, 0.001241662656

};

static float32_t FIR_DATA_TEMP_F32[BLOCK_SIZE + FIR_COE_LEN - 1];

arm_fir_instance_f32 S_F32;

void fir_init_f32(void){

arm_fir_init_f32(&S_F32, FIR_COE_LEN, &COE_F32[0], &FIR_DATA_TEMP_F32[0], BLOCK_SIZE);

}

void fir_f32(float32_t *in, float32_t *out){

uint16_t i;

for(i = 0; i < FIR_TIMES; i++){

arm_fir_f32(&S_F32, in+(i*BLOCK_SIZE), out+(i*BLOCK_SIZE), BLOCK_SIZE);

}

}信号调制

FM调制的本质是通过输入模拟信号的幅值去控制载波频率,进而实现通过频率去携带原始信息的目的。一个典型的模拟域FM调制系统常常是通过控制VCO或者PLL来实现频率的调制;数字域FM调制系统往往是通过操作DDS实现的,由于DDS可以实现频率与相位的突变,因此只需建立输出频率与幅度的关系即可。

调制原理

一个典型的FM信号$s_m(t)$可以表示为下式,其中$A$表示恒定不变的幅度信息,$\omega_c$表示载波频率,$\varphi(t)$表示信号相对于载波的瞬时相位偏移。

$$ s_m(t)=A \cos \left[\omega_c * t+\varphi(t)\right] $$

对频率的调制本质上就是信号瞬时频偏$\frac{d\varphi(t)}{dt}$相较于调制信号$m(t)$成正比例变化,即有调频灵敏度$K_f$描述如下式。

$$ \frac{d\varphi(t)}{dt} = K_f*m(t) $$

规定调频指数 为信号频偏相较于调制信号频率的比例,即规定如下式。

$$ m_f=\frac{K_f*A}{\omega_m}=\frac{\Delta f}{f_m} $$

FM调频根据调频指数的大小可以划分为宽带调频与窄带调频,调频信号带宽与调频指数、原始调制信号频率有关。根据卡森公式,一个典型的调频波信号带宽可以表述为下式。

$$ B_{FM}=2(m_f+1)f_m=2(\Delta f+f_m) $$

工程实现

在前文架构设计时,我们已经确定了发射部分的架构采用低中频架构。对于单片机而言,由于调节DDS输出的信号频率来调制需要很高的中断频率去更新DAC数值,因此在此直接通过操作IO口输出PWM波的频率来实现调制。借助STM32的片上硬件定时器,我们可以实现几乎无干预的FM调制,我们要做的仅仅是在ADC3采样数值更新时更新PWM频率,该数值的更新频率仅为10KHz,大大减小了单片机的处理压力。

单片机产生PWM波形主要通过硬件定时器实现,引出PWM Generation CHx通道即可实现PWM信号在GPIO上的输出。一个典型的PWM波形包含三个参数,其中幅值由GPIO决定,固定为3.3V;频率由分频系数$PSC$、自动重装载值$ARR$决定;占空比由$Pulse$决定。由于FM调制波形中只有频率信息携带了原始信号,故在此不再关注幅值与占空比两个参数,只对$PSC$与$ARR$进行修改即可。

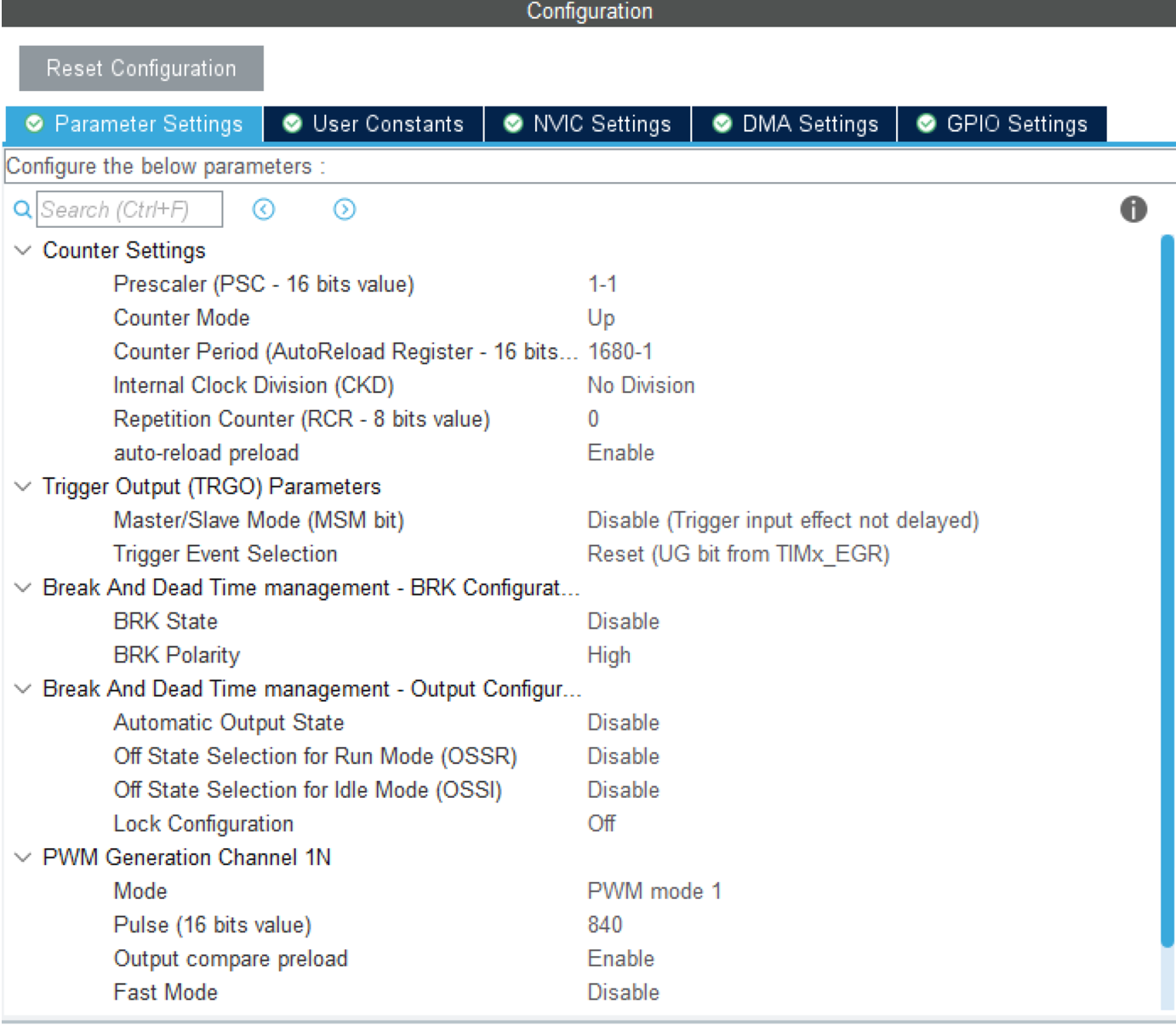

为了实现较低的调频系数,在此选用工作频率168MHz的TIM8用作PWM生成定时器。当指定$PSC=0$时候,PWM波形的频率完全由$ARR$决定。当指定中频频率为100KHz时,$ARR$取得1679,因此对FM的调制完全映射到对$ARR$数值的修改,对工程中定时的配置举例如图4-10所示。

故我们可以直接通过ADC采样的数据对$ARR$数值进行修改,具体的工程代码举例如下。

void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef *hadc){

if(ADC3 == hadc->Instance){

pwm_temp = HAL_ADC_GetValue(&hadc3);

pwm_temp = pwm_temp >> 4;

if(pwm_temp >= 128){

__HAL_TIM_SET_AUTORELOAD(&htim8, 1680 - (pwm_temp - 128));

}else{

__HAL_TIM_SET_AUTORELOAD(&htim8, 1680 + (128 - pwm_temp));

}

}

}在上述工程代码中,当ADC3采样数值高于$\frac{VDD}{2}$时提高PWM频率,当ADC3采样数字低于$\frac{VDD}{2}$时降低PWM频率。故可以通过计算得到ARR的范围为1552-1808,对应的PWM频率范围为92.92KHz-108.25KHz。由于基带信号的频率范围为0-3.4KHz,故可以得到本方法调制FM信号的调频指数$m_f$为:

$$ m_f=\frac{100-92.92}{3.4}=2.08 $$

由于部分非线性因素的引入,所以造成信号的质量的略微降低,但对于人类的听觉而言这样的信号质量下降无明显听感差距。

5、测试验证

条件所限,本节所使用到的测试仪器都较为业余(示波器DS100、网分NanoVNA、信号源ADALM2000),只有定性分析的意义,故此节不做摘录。下文仅列举一些需要测试的指标:

- 接收机滤波器幅频特性:MSI001的前端滤波器通阻带幅频特性,分析是否满足设计要求;

- 接收机基带信号波形:通过MSI001调谐完成的基带信号波形,送入MATLAB解调验证可行性;

- 发射机的载波信号频谱:评估发射机部分的载波频谱质量;

- 发射机的基带调制信号:进行模拟、数字调制时的基带信号波形与频谱;

- 传输线阻抗:通过Smith圆图测量传输线阻抗,验证传输线阻抗的设计流程;

- 天线驻波比:通过选取合适频段的天线来规避额外损耗,提高传输效率。

本设计的实物图展示如下:

6、总结

本设计通过单片机、调谐器、本振、混频器等元件实现了一个软件无线电平台,该平台具备完整的无线电收发功能。接收部分的架构为零中频架构,采用集成调谐器实现信号的下变频到基带,基带部分通过单片机实现FM模拟调制信号的解调、下采样、滤波与输出;发射部分的架构为低中频架构,中频频率100KHz。采用STM32定时器对采样到的模拟信号进行调制,并使用锁相环作为本振信号,基带信号通过混频器实现信号的上变频。

设计流程大致分为需求定义、架构确定、元件选型、理论分析、设计仿真与测试验证等六个步骤,这些步骤也是一个典型产品的开发流程。其中需求定义部分要求设计一个软件无线电收发系统,并要求成本低廉与开发便捷;架构确定部分通过对比工业上典型的无线电架构,以选择出一种或几种最适合本设计的架构,即零中频+低中频架构;元件选型部分综合考虑成本、可开发性与供货量最终敲定所用元件;理论分析部分涉及采样定理、滤波、混频等诸多流程的理论分析,这些理论都为后文的设计仿真与验证提供了基石;设计仿真部分主要使用计算机进行辅助设计与仿真,利用计算机辅助可以极大地提高设计效率并减少出错;测试验证涉及设计的投产与仪器的指标测试,最终通过性能指标等客观因素来确定设计成功与否。

然而,受限于设计成本、开发周期、仪器使用等诸多因素,本设计仍存在诸多的缺陷。譬如受限于芯片算力,尚未实现收发的全双工模式;受限于仪器使用限制,所有指标只能用来定性分析而无法用作定量分析;受限于成本因素,元件的容限误差导致接收机链路滤波器的幅频响应不太理想

整个架构的设计合理、功能完整、开发便捷,达成了本设计的最初目标。