基于NRF7002-DK实现的NFC原神启动器!

本项目的设计目的是借助nRF7002-DK的板载NFC功能实现卡片模拟,当手机靠近NFC天线时能读取到卡片中存储的字符信息,板卡同时点亮LED1灯表示NFC通信正在进行;板载的按键可以在纯文本传输与启动APP之间切换,板卡通过LED2指示当前的工作模式。

硬件信息

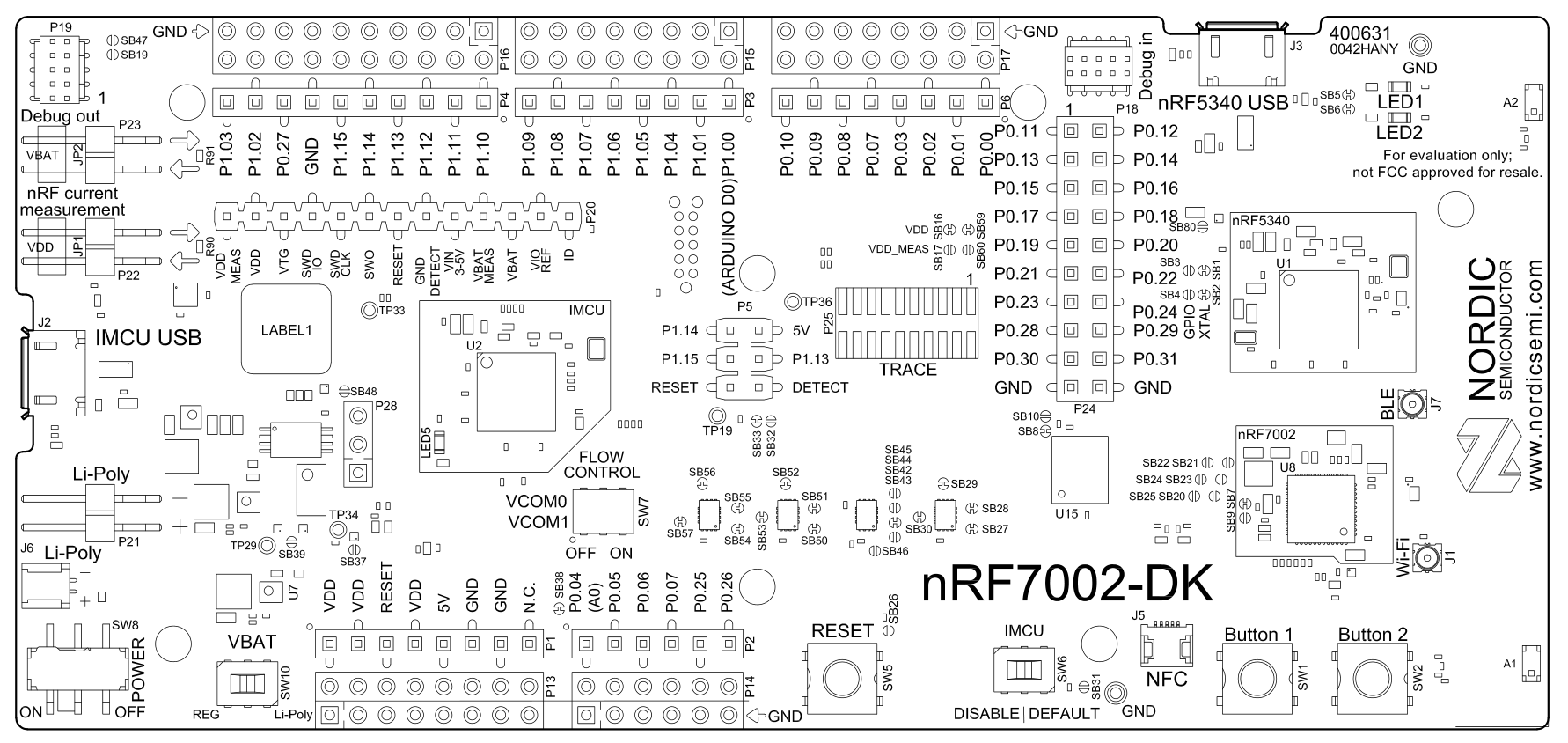

nRF7002-DK板载三颗MCU芯片,其中一片nRF5340用作接口MCU,刷写有Jlink固件提供调试下载与虚拟串口的功能;一片nRF5340用作主MCU,用于用户逻辑的实现;一片nRF7002用作协同MCU,处理Wi-Fi相关的事务,并与主MCU之间通过QSPI进行通信。

上图即为本板卡的俯视图,其中U2为接口MCU,U1为主MCU,U8为协同MCU。同样地,板卡上板载了三个天线接口J1 J5 J7与两个板载陶瓷天线A1 A2。其中J5为NFC天线接口、J1为WiFi天线接口、J7为蓝牙天线接口、A1为2.4G/5G双频天线、A2为2.4G单频天线,用户可以根据需求配置射频选择器来选择天线使用。

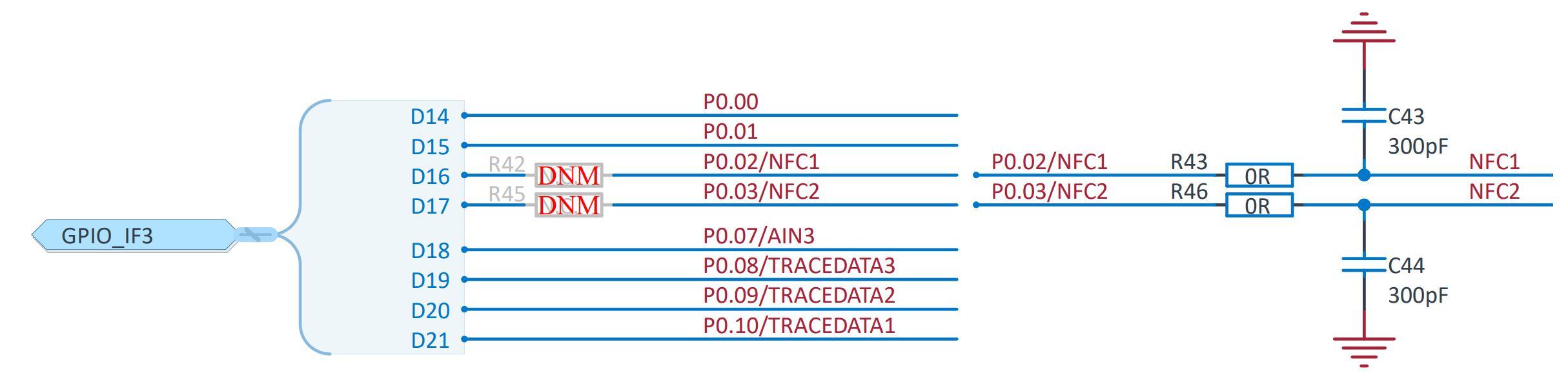

本设计中的关键内容是NFC部分的硬件连接与配置,通过查阅硬件手册的4.13章节得知NFC天线默认连接在P0.02与P0.03两个引脚。这对引脚的默认功能被配置为NFC,如需使用为GPIO需要配置prj.conf并修改硬件电路。相关电路图如下所示,在此只使用NFC功能不对硬件做修改。